功能模块

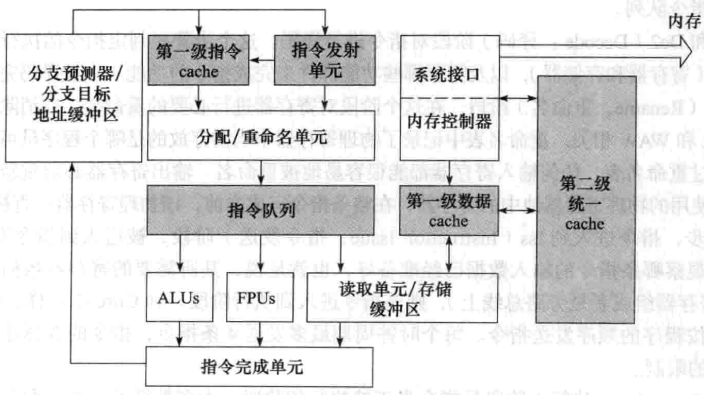

OMAP4430上有2个ARM Cortex A9处理器核心,使用ARM v7指令集。该核心是32位的,使用32位的寄存器、数据通路、存储总线。与INTEL酷睿处理器不同,该核心是真正的RISC处理器,其使用的指令本身就是类似于微操作的。上图为其大致的组成。

A9比酷睿的微体系结构简单很多,但两者的关键部件有很多相似的地方。比如A9也使用了两级的高速缓存,但其L2缓存只有1MB。L1指令缓存是32KB的四路组相联结构,块大小为32字节。由于大多数ARM v7指令是4字节的,所以L1指令缓存可容纳8K条指令,比酷睿的微操作缓存的容量要大。L1数据缓存也是32KB的四路组相联结构,块大小为32字节。

指令发射单元每个时钟周期能至多发射4条指令。遇到条件分支时会根据4K个表项的分支预测器判断跳转是否发生,如果预测发生,再去1K个表项的地址缓冲区判断跳转的目标地址。如果前端发现程序正在执行“紧凑的小循环”,会把循环装入快速循环旁路缓存,用于优化速度和能耗。

指令进入分配/重命名单元和指令队列后,和酷睿一样会使用寄存器重命名等技术,让指令乱序执行。指令队列接着把指令送入功能单元,其中ALUs包含2个整数ALU和1条短的处理分支的流水线,FPUs包含1个可选的VFP浮点单元和1个可选的NEON整数向量单元,A9不一定必须包含这2个单元。

读取单元/存储缓冲区用于处理存储器的读写指令,其中存储缓冲区用于支持类似酷睿I7的存储-加载转发的过程。OMAP4430还包含控制内存访问的逻辑,包括系统接口和内存控制器两部分。系统接口通过32位LPDDR2总线连接内存,该总线支持26位字地址(字长32位),内存被划为8个BANK。OMAP4430包含2个独立的LPDDR2通道,每个通道理论可寻址2GB的空间。内存控制器用于将内存的虚拟地址转换为物理地址,因为A9支持虚拟内存。为了加速映射过程,会采用旁路转换缓冲区(TLB)直接缓存一部分虚拟地址对应的物理地址。为了区分指令和数据,这个表有2个。

流水线功能

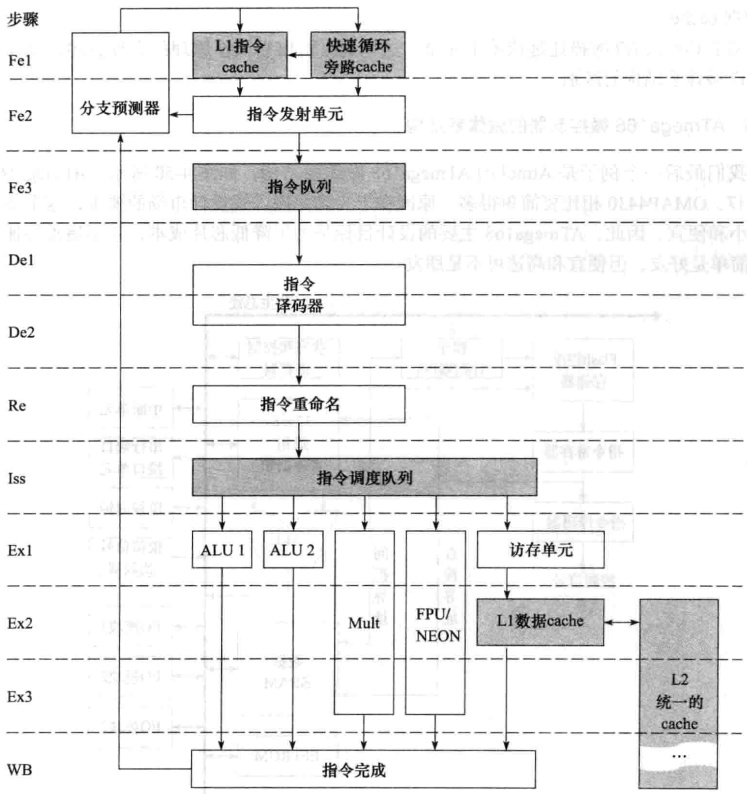

A9有一条11段的流水线,上图是该流水线的简化版。