功能模块

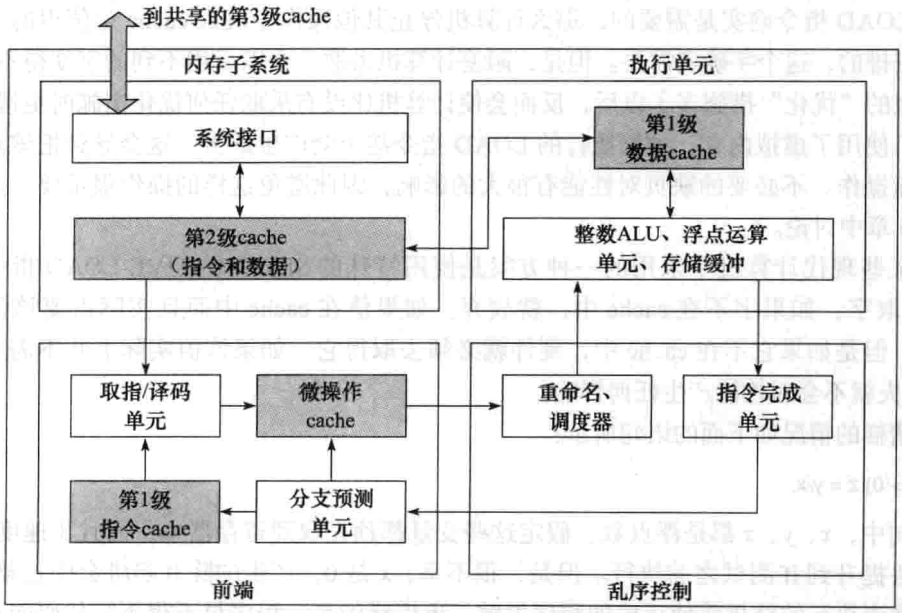

上图为酷睿I7的每个核心的组成结构,其包括如下4大部分:

1) 内存子系统:内存系统的一部分,不包括核心外的L3缓存、主板上的内存;

1.1) L2缓存:不区分指令和数据,为256KB的8路组相联结构,缓存块大小为64字节;

1.2) 系统接口:连接到L3缓存,L3缓存也不区分指令和数据,大小为1-20MB(根据产品型号确定,比如i5、i3等),采用12路组相联结构,缓存块大小为64字节。L3缺失时继续访问DDR3内存总线;

L1缓存和内存子系统间存在未画出的2个预取单元,第1个是按内存块大小预取的。第2个是按步长预取的,当CPU总以连续的k个地址(步长)取数据时,该预取单元会获取到这个步长,并根据这个步长预取数据,这种预取策略考虑的是便于操作数组等数据结构。

2) 前端:取指令并将指令译码为微操作序列,酷睿的微操作和RISC处理器的微操作风格类似。并且能够把译码前的指令装入L1指令缓存,把译码后的微操作装入微操作缓存(INTEL内部称为L0缓存);

2.1) L1指令缓存:32KB的8路组相联结构,缓存块大小为64字节;

2.2) 微操作缓存:有足够空间保存每个指令的微操作。除了提高流水化程度,还能降低功耗;

2.3) 分支预测单元:进行分支预测,并根据预测结果控制微操作的输出等。在商业CPU中,分支预测技术是性能的最关键因素,所以具体的分支预测策略是商业机密;

3) 乱序控制:控制指令的乱序执行和按序完成;

3.1) 重命名/调度器:接收微操作缓存输出的微操作序列(指令),并乱序执行微操作;

3.2) 指令完成单元:酷睿i7支持精确中断,指令要按序完成。该单元用于实现按序完成;

4) 执行单元:包含多种多个可并行工作的ALU等部件,所需的数据来自寄存器和L1数据缓存;

4.1) L1数据缓存:32KB的8路组相联结构,缓存块大小为64字节。其使用拖后写策略,块被置换时才写回到L2。L1数据缓存允许在1个周期里处理2个读和1个写。这通过分体技术(Banking)实现,缓存被分为8个Bank,3个读写只有作用于3个不同Bank才能在1个周期里同时进行;

流水线功能

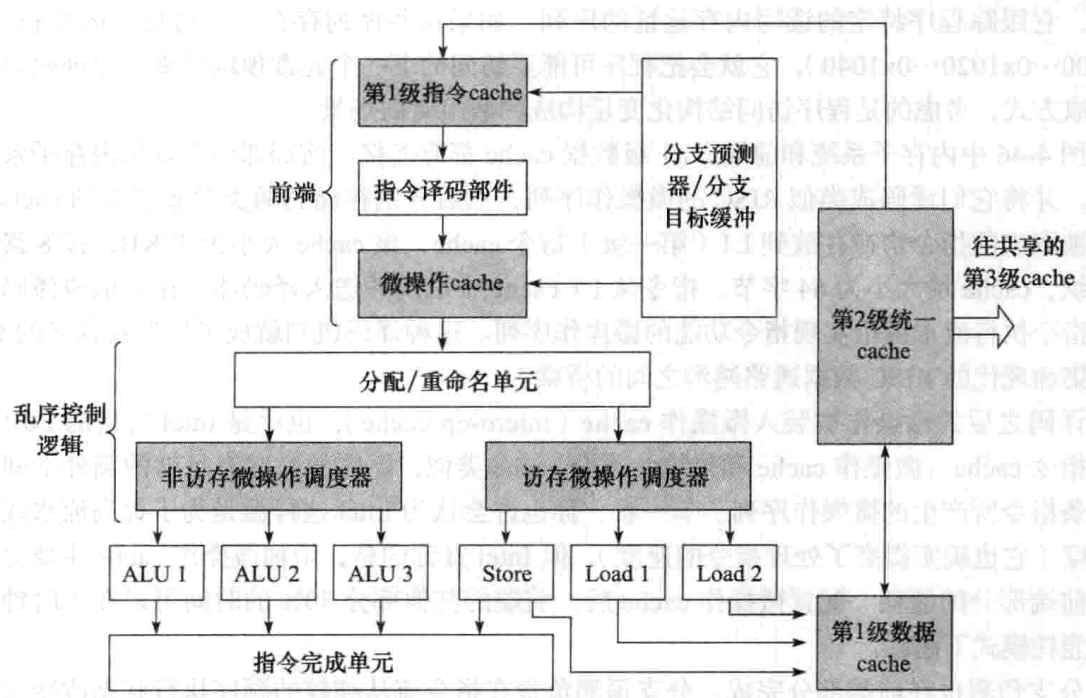

上图为该CPU流水线功能的简化版,其第一部分为前端。首先L1指令缓存接收内存子系统传出的指令,指令译码后被装入微操作缓存,其能存储1.5K个微操作。微操作缓存的基本单位为6个微操作组成的跟踪块,1条指令可对应多个顺序的跟踪块。译码单元遇到条件分支会做分支预测,其由2个部件支持:

1) 分支预测器:存储指令的跳转历史,如果译码单元在此查到了相应指令的跳转历史,就用“保密的动态分支预测策略”预测是否跳转。如果没有查到就用静态分支预测,静态预测的策略是之前提过的“向后跳转一定发生”和“向前跳转一定不发生”,其中前者准确率很高,后者准确率低;

2) 分支目标缓冲器(BTB):存储指令上次跳转的目标地址,译码单元预测跳转时会跳至这里记录的地址。这个地址对if和循环通常是正确的,但switch的目标地址可能不止1个,所以可能会预测错误;

3) 分支顺序缓冲器(BOB):图中未画出。分支预测失败时用于“回滚”计算机状态;

流水线第二部分是乱序控制逻辑。分配/重命名单元中包含如下2个重要部分:

1) 重排序缓冲区(ROB):包含168个表项,每项记录1个微操作的状态,以及该微操作原本的执行次序。每个表项都被维护着,直到其对应的微操作执行完;

2) 寄存器关联表(RAT):用于寄存器重命名时记录映射关系;

分配/重命名单元能在1个周期至多接收4个微操作,并将它们记录到ROB,此时微操作尚未被打乱次序。而对于ROB中的微操作,分配/重命名单元先是会通过寄存器重命名避免一部分ROB中的微操作与正在执行的微操作有WAR/WAW相关,但如果这之前就已经没有空闲的物理寄存器用于寄存器重命名、或是存在RAW相关,那么会在ROB记录这些“问题”,相应的微操作也暂时不被传入调度器。所以每个微操作进入调度器时都与正在执行的微操作没有相关。更进一步,调度器中的所有微操作都可乱序执行。这是因为前面提到过,不存在相关的两个指令是完全可以不分次序的并行的。基于这一点,这2个调度器会尽量在每个周期输出3+3个微操作给这6个执行部件,这6个部件都可并行工作。

然后看这6个部件的组成和功能。其中3个ALU都包含整数ALU和浮点计算单元,ALU3还包含分支控制单元。这3个ALU能实现整数、向量、浮点数的算术和逻辑运算,以及分支控制。但这3个ALU并不相同的,比如只有ALU3能做分支控制,而ALU1~3都能做算术运算,但它们3个支持的算术运算种类又是不同的。Load1/Load2用于执行读存储器,Store用于执行写存储器。

ALU中的整数ALU和浮点计算单元是分别从2个寄存器组获取操作数的,即浮点数和整数的寄存器是不通用的。ISA寄存器也是由该寄存器组提供的。Sandy Bridge架构相比于上一代的酷睿架构,引入了AVX指令集。可支持最高256位的向量整数、向量浮点数的运算。但该CPU的数据通路宽度是128位并未支持到256位,INTEL通过把256位运算拆分成2个128位运算,同时送入2个ALU来实现这样的运算。

前面提过微操作是乱序发射的,但指令必须顺序完成,因为要支持精确中断。那么指令中的写存储器微操作必须等到指令完成单元确认该指令前的指令都已完成后,才能实际写入L1数据缓存(内存系统),否则中断发生时,无法保证中断后的指令没有影响到计算机的状态,也就是没有实现精确中断。那么为了支持精确中断,被乱序发射的写存储器微操作不能马上写入L1数据缓存,而是把写入结果放入待定存储缓冲区(包含36个项)。由于这只是为保证某些提前执行的微操作不影响到顺序执行和精确中断,所以如果之后有读存储器微操作试图访问这部分数据时,其应当能从待定存储缓冲区读到这部分数据,虽然它们还不在数据L1中。这样能更好的发挥乱序执行的能力。这样的“写入-读取”过程称为存储-加载转发。

实际上,实现存储-加载转发会非常复杂,因为有些存储可能还没计算出其存储到的地址,从而不知道应该转发待定存储缓冲区中的哪一项,确定哪一项的过程称为相依性猜测。可以发现,如果需要考虑到访存微操作和缓存,乱序执行的控制会变得十分复杂。该CPU本身也是非常复杂的。