MIC-4的流水线

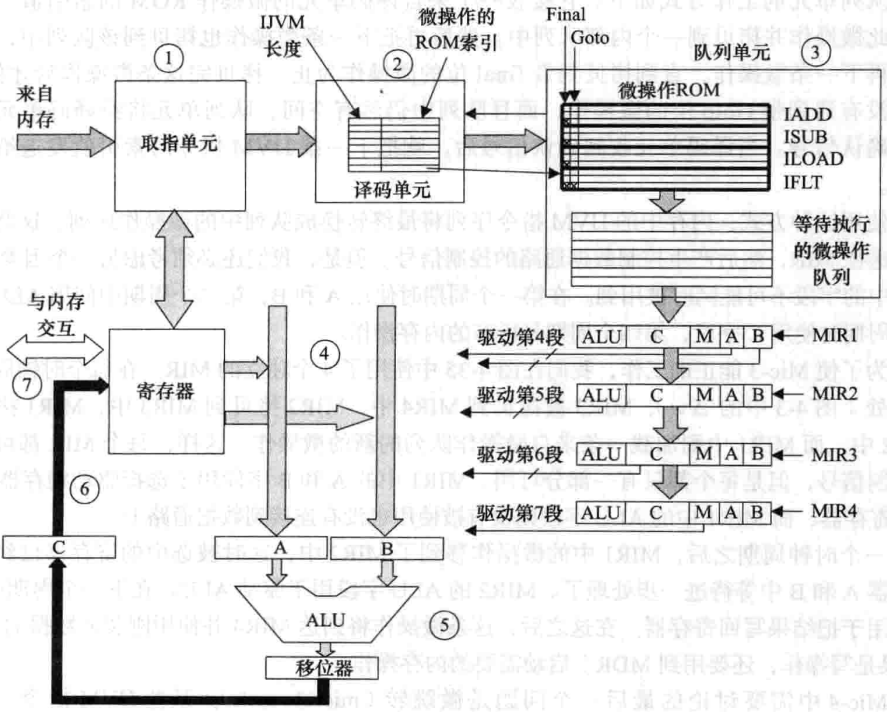

MIC-4是对MIC-3的改进,其具有更深的流水线。其使用和MIC-3相似的数据通路和IFU,并引入新功能单元。上图是MIC-4的结构,图中没太多细节,简单了解各功能单元即可:

1) 译码单元:用于划分出包括操作数和操作码的整条指令。其组成包括一个内部ROM,其索引为操作码,数据为指令长度与队列单元的微操作ROM的索引。记录指令长度可能是为了避免误把操作数当操作码。有了译码单元处理WIDE指令就会更方便,可以直接把WIDE ILOAD作为整体映射到微操作ROM;

2) 队列单元:其组成包括1个ROM表和1个RAM队列,前者存储微程序,后者暂存微操作;

2.1) 微程序: MIC-4的微程序结构不同,每个ISA指令对应ROM表的一些顺序的行,这些行称为微操作,其类似于微指令,但微操作大都不含“下个微操作的索引”,所以对于ILOAD和WIDE ILOAD,它们各自的微操作序列里有重复部分(不再有MIC-2那样从wide_load2跳到wide的技巧)。微操作包含FINAL位和GOTO位,前者表示这是微操作序列的最后一条,后者类似于微指令的条件转移。FINAL或GOTO为1的微操作的内容是不同的,其中包含微操作索引和类似MIC-1中的JAM的内容,这意味微操作不能像MIC-1微指令那样在一条里执行数据通路操作和条件转移(比如iflt4),要拆分作为两类微操作才行;

2.2) 微操作队列:译码单元指定ROM表索引后,ROM表会把从索引处的微操作到有FINAL位的微操作之间的所有微操作拷贝并入队到微操作队列中。拷贝时如果没遇到有GOTO位的微操作,且拷贝结束后队列中还有足够剩余空间,那么队列单元会“通知”译码单元发送下一个指令的微操作ROM的索引;

3) MIR1~4:由4个结构一样的MIR组成,4个MIR用于控制数据通路上的4个时钟周期,每个时钟周期开始时,队头的微操作进入MIR1、原MIR1的微操作进入MIR2、原MIR2的微操作进入MIR3….,也就是说对于1个微操作,其在MIR1-MIR4中都是只有一部分信号是有效的。可以发现可能出现一部分MIR中的是指令A的微操作,另一部分MIR中的是指令B的微操作;

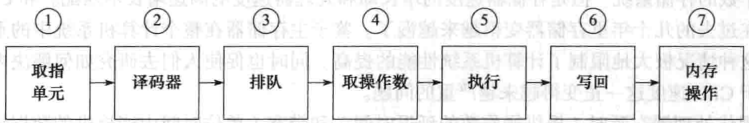

MIC-4的结构跟INTEL酷睿I7有点点相似,上图第二张为MIC-4的七段流水线,这七段甚至会使用不同的时钟。MIC-4的功能单元、功能单元间的关系都很复杂,这里无法分析它们的具体组成和工作时序,大概理解这个7段式流水线就行。MIC-4比MIC-3更加流水化,假设多个ISA指令都完全流水线式的执行,那么同时是会有多个ISA指令在流水线上的,也就是MIC-4可以让多个ISA指令“并行”。

另外根据该数据通路以及流水线的特点可以发现,一条指令只有走到阶段6后,才会产生“效果”,因为只有此时改变寄存器/内存的数据,对计算机产生实质的影响。换句话说如果流水线上某条指令尚未进入阶段6,那么将该指令和其后面的所有指令(在流水线上的)全部清空就相当于这些指令从未进入过流水线。在一些情况下,计算机不得不做这种清空流水线的操作。