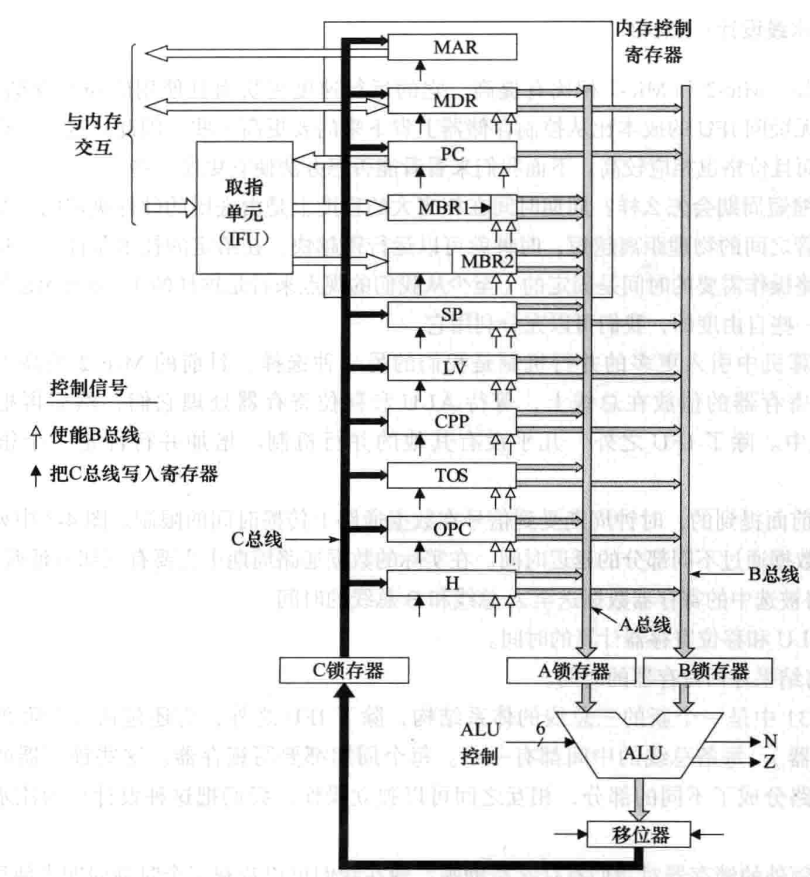

MIC-3的数据通路

前面讨论了比MIC-1更快的MIC-2,但由于使用了IFU,MIC-2的成本比MIC-1更高。接下来继续讨论如何把MIC-2改进成速度更快的MIC-3,改进基于如下2个方面:

1) 缩短时钟周期:通过改进电路缩短周期,虽然集成电路技术对这方面作用更大,前面提过这点;

2) 提高并行度: MIC-2虽然比MIC-1有更大的并行度(IFU并行取指),但其并行度仍可继续提升;

集成电路水平给定时,MIC-2允许的最短时钟周期很大程度由3部分延迟的和决定:

1) 寄存器数据通过A、B总线的延迟;

2) 数据通过ALU、移位器的延迟;

3) 数据通过他总线(写寄存器)的延迟;

上图为了MIC-3的数据通路,相比MIC-2仅多了3条总线上的3个锁存器。这可以让数据分3个时钟周期通过数据通路,第1个周期寄存器把数据送入A、B锁存器,第2个周期把计算结果送入C锁存器,第3个周期让C锁存器写入寄存器。表面上看,数据通过数据通路的时间扩大到3个时钟周期,但由于这3个步骤的总延迟与之前1个步骤的延迟差不多,所以可认为MIC-3能使用快3倍的时钟(理想状态)。

这个改动如果只是这样,那就是多此一举,并且就算用上了快3倍的时钟还是会比MIC-2慢一点。而这个改动所带来的最大进步是这3个步骤是可以并行的。比如在某个周期里需要让数据写入A、B锁存器,但ALU还可以在该周期里用上个阶段的A、B锁存器的数据做计算。

为了方便讨论,这里将MIC-3数据通路上的顺序执行的3个步骤统称为1个微操作步。另外这个数据通路不再是单周期数据通路了,而是多周期数据通路。

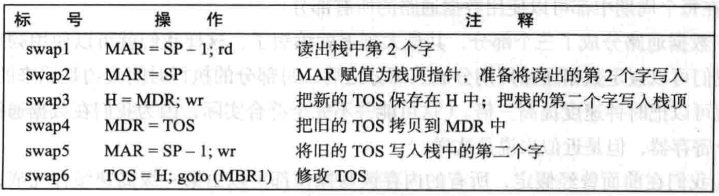

MIC-3的微程序

上图第一张是MIC-2的SWAP实现,第二张则是MIC-3的SWAP实现以及与MIC-2微指令的对照,其中前两行描述两者对照关系。为了更好的描述“并行”,MIC-3采用了二维表格描述微指令,每列表示原MIC-2微指令对应的微操作步。在MIC-3执行SWAP执行需要11个时钟周期,MIC-2需要6个,如果让MIC-3的时钟快3倍,那么整体上MIC-3能够快1.6倍左右,因为其能让多条微指令“同时”执行。

在MIC-3的微汇编中,锁存器被作为寄存器对待,可像其他寄存器那样参与“赋值”和“运算”。另外在内存操作完成时,会进行显式的说明,比如swap1列的4行表示上个周期read的数据写入MDR,swap3列的8行表示上个周期的write已经写入内存。最后要留意的是ALU用于直通和自增时,另一输入端是没有使能的(ALU的控制信号线有使能线),所以这时不用考虑对另一端的处理。

可以发现swap1/swap2能在MIC-3中“高度”的并行,两个微指令几乎同时开始、结束。但swap3则与swap1是完全串行的,这是因为swap3在一开始就需要swap1在结束时取回的数据,所以只能这样安排swap3。这种因为需要等待上个操作步的结果而不能启动下个操作步的情况被称为真相关或写后读相关(RAW相关)。而相关属于一种流水线的冒险。

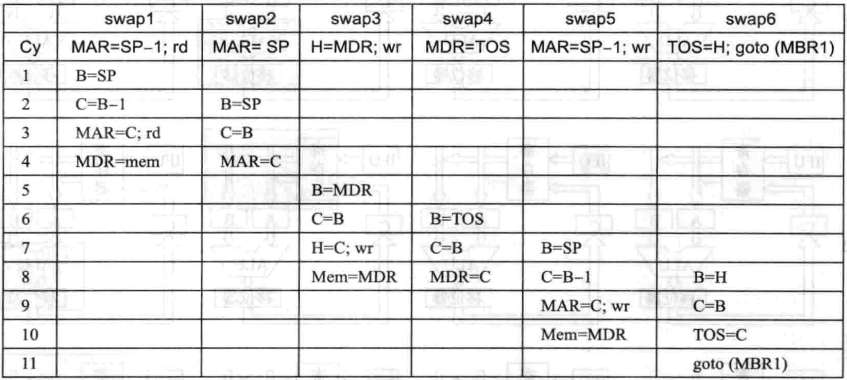

MIC-3的流水线

流水线是所有现代CPU都使用的关键技术之一,上图更直观的描述了MIC-3数据通路上的流水线。图中设定了有4条指令需要执行,每条指令都需要4个周期,指令之间没有相关,其中从左到右的列为第1-4个周期,从上到下的行为第1-4条指令。可以发现从第4个周期开始,每个周期都有一个指令被完成。

CPU的流水线就类似于工厂里的流水线,比如某工厂有1条流水线是用4个步骤组装商品的,流水线上有4个工人,每个人专职负责1种步骤。假设这个流水线1分钟移动1格(1个工位),那么在第4分钟结束后,每分钟就会有一个商品从流水线中出来。

MIC-3的流水线功能是比较简单的,其能够让单个指令对应的多个微指令“并行”,但是其无法让多个指令对应的多个微指令“并行”。因为在MIC-3的微程序中仍以多路跳转(goto (MBR)等)开启下个指令,而goto (MBR)往往是最后一个微指令中的操作,即只有指令在执行完后才开始下个指令。让指令“并行”比让同个指令中的微指令“并行”困难,指令中有哪些微指令是确定的,“编写”微程序时就能确定微指令间的“并行”关系和相关。但指令的执行完全是动态的,下一条指令是不确定的。