取指单元(IFU)

回顾MIC-1微体系结构,可发现两个导致占用过多时钟周期的问题点:

1) 需要一次一字节的取操作数,并且还16位操作属还需要拼接。其中每取一个字节都对应于一次ALU的占用(一个时钟周期),因为其需要PC自增来提供内存地址。拼接过程同样如此;

2) ALU在很多时候并未用作“复杂”的算术逻辑计算,比如最简单的是让数据“直通”,其次是自增。其相对于ALU的面积是种浪费,且和复杂的ALU计算占用相同时间;

基于上述原因,可以考虑在MIC-1加一个面积小且能力弱的ALU,其“位置”和ALU类似,能和ALU并行工作于同一时刻。该方法能平衡面积(价格)与速度的矛盾,因为其用较少面积“分摊”了一部分的ALU占用时间。这种思路下的具体方案就是在MIC-1加入IFU(取指单元)。IFU通常基于2种预取策略:

1) 能解释操作码,从而知道接下来取几个字节,并把它们都装入寄存器;

2) 总是使之后的若干个字节处于寄存器中,但不去管这些字节的具体意义;

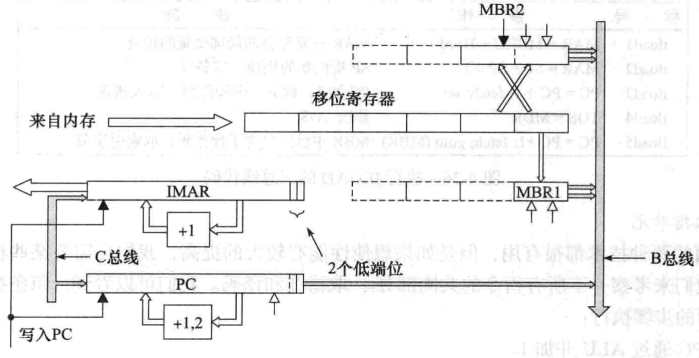

上图是基于(2)的一种IFU,其部件有的对数据通路“可见”,有的则“不可见”。首先讨论数据通路“可见”的寄存器MBR1、MBR2、PC。其作用与原MIC-1的PC、MBR相对应,其中MBR1为8位、MBR2为16位,都支持32位的符号扩展和无符号扩展。区别在于这3个寄存器都会“自动更新”,规则是这样,假设此时MBR1保存了内存第1个字节,MBR2保存了第1,2个字节(从左到右)。读取MBR1,MBR1之后自动更新为第2个字节,MBR2之后自动更新为第2,3个字节,PC之后自动自增1。同理读取MBR2,MBR1之后自动更新为第3个字节,MBR2之后自动更新为第3,4个字节,PC之后自动自增2。

上述“自动更新”是基于“不可见”的IMAR寄存器和6字节移位寄存器。前者指定内存地址,后者存放取回的内存数据,并以队列形式提供给MBR1/MBR2。然后看移位寄存器和MBR1/MBR2是如何协作的,假设此时移位寄存器已有第1-6个字节(从右到左),那么MBR1必须跟队头一样为第1个字节,MBR2从左到右必须为第1,2个字节。如果MBR2被读取,那么移位寄存器自动出队2次,并用新的前2个队头更新MBR1/MBR2。当移位寄存器只剩0~2个字节,就可根据IMAR按字读内存,然后让读回来的4字节入队。

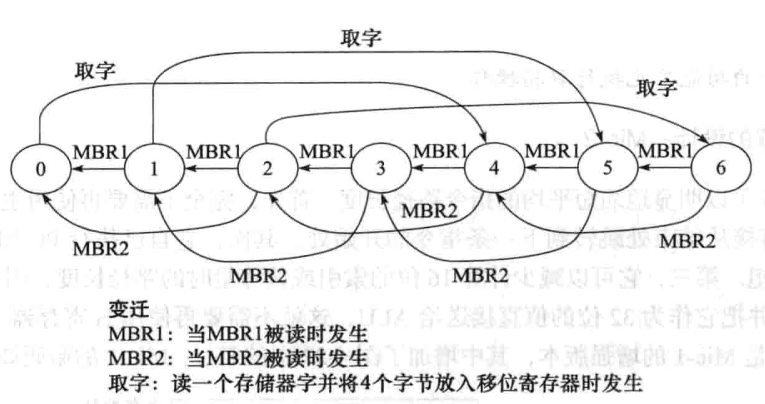

上图第二张是详细描述上述过程的有限状态机(FSM),白色圈圈(状态)为移位寄存器的剩余字节数,箭头(转移)表示允许的操作,操作会改变状态(状态转移)。实际情况更复杂,比如还要考虑到跳转操作直接改变PC,IFU必须监听C总线并捕获PC写入的新值,但IMAR使用字地址,且新PC无法保证在字的开头。所以IFU不仅要算出字节所在的字,还要调整移位寄存器使PC成为队头。可以发现IFU在遇到一些事件时需要分多个步骤处理(比如前面这种),但IFU只能串行处理事件,下个事件须在上个事件处理完后到达。

MIC-2的数据通路与微程序

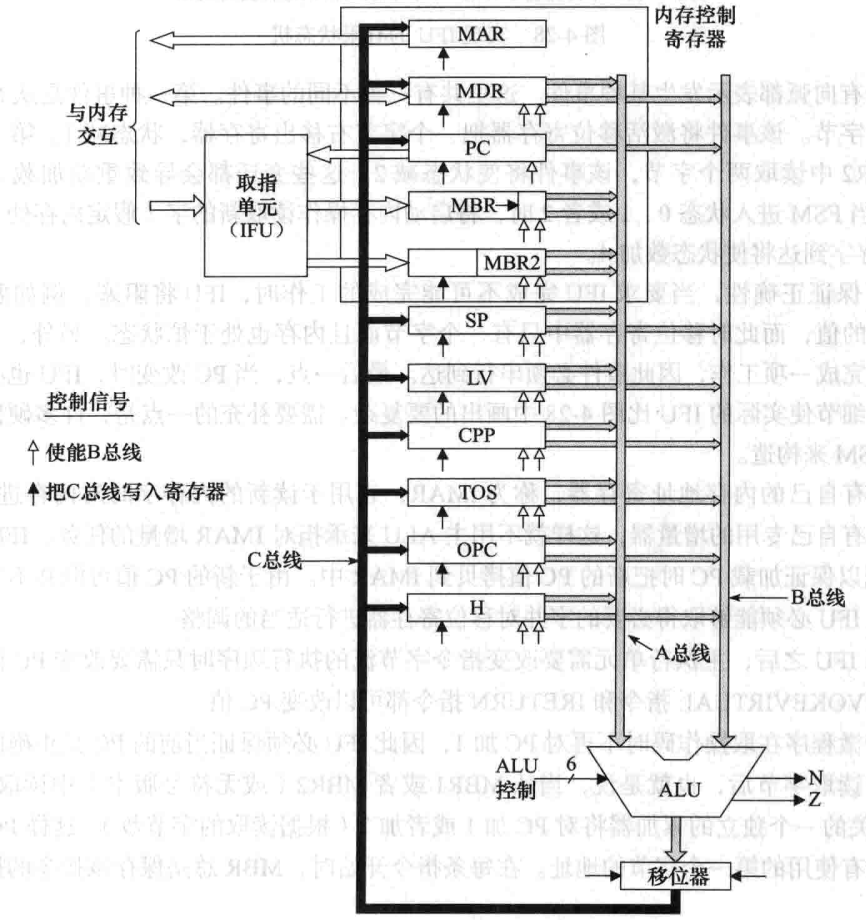

上图的第一张是MIC-2的数据通路,其相比MIC-1加入了IFU和A总线。MIC-1的微程序主循环外只有内存操作,而MIC-2加入的IFU能让主循环外有更多的操作,从而每个循环节中的操作和时间就减少了。由于MIC-2中多了A总线,所以MIC-2的控制部分和MIC-1有区别,但接下来不会分析MIC-2的控制部分,以及微指令中的各个位,而是直接沿用微汇编的形式讨论实现IJVM的微程序。

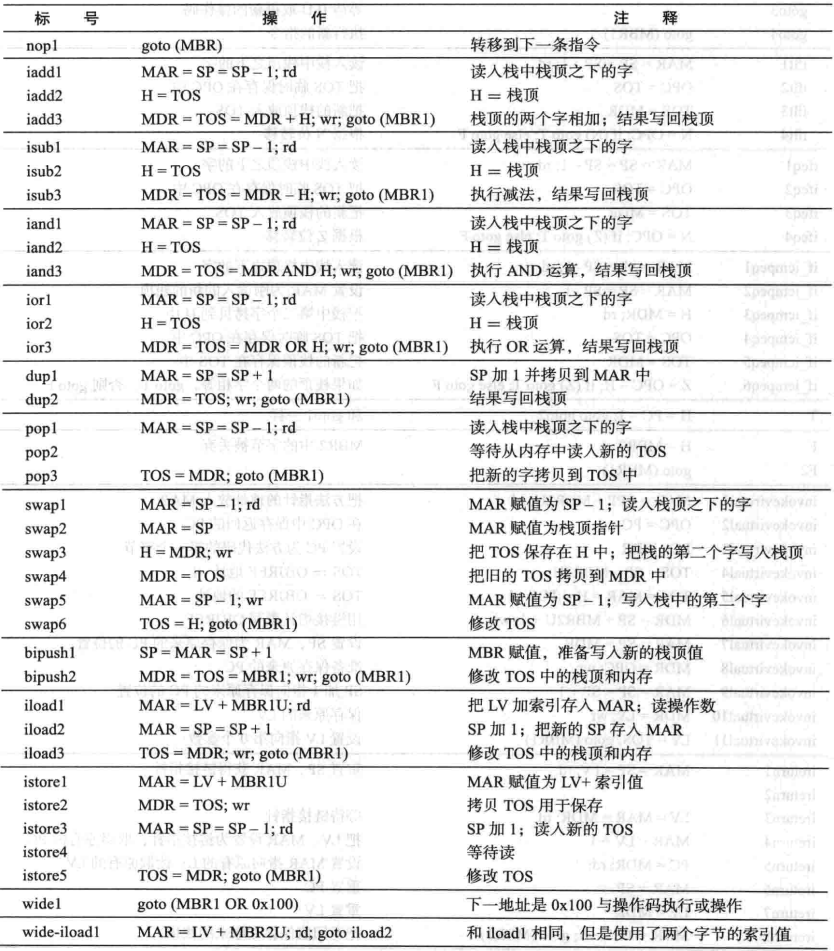

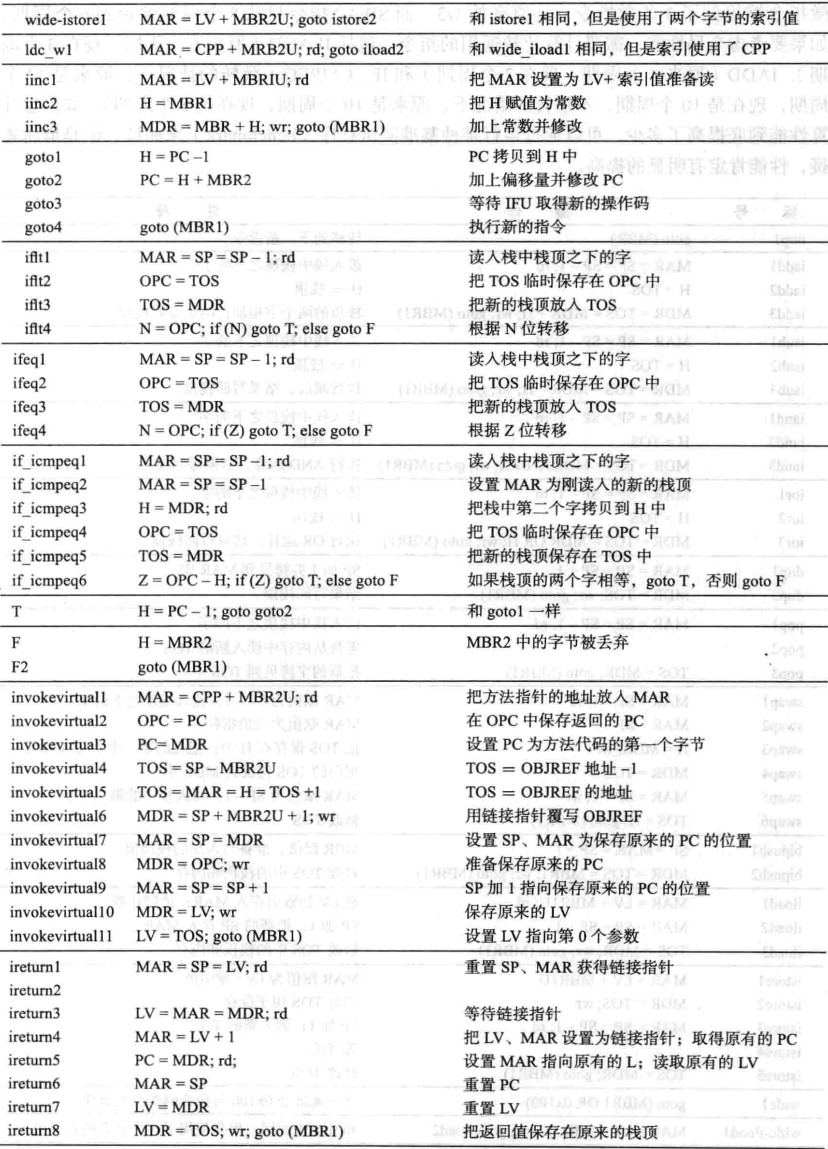

上图的第二张是IJVM指令的MIC-2实现,其除了加入IFU外还整合进了前面文章所提到的优化点,即合并主循环与微指令、三总线结构下的快速加法。并且得益于MBR2寄存器,无需拼接16位操作数,可以发现不少指令的时钟周期数(微指令数)相比MIC-1都有不同程度的减少,也就是MIC-2有更快的速度。

对MIC-2的讨论就先到这,虽然还剩下不少IFU的细节没讨论,比如其控制信号、时序等。