速度与价格

商用CPU的优化问题主要集中在对速度(性能)与价格(成本)这对矛盾的权衡,更高的性能往往意味着复杂的电路和更多的部件,进而需要更大面积,这又会导致功耗和散热难度的增加和芯片良品率的降低,也就是成本的增加。而且面积并不能无限增大,这会导致部件的电气性能变差,反而降低性能。所以如何合理利用面积也是个重要衍生问题,比如加法器曾有千种设计,速度快的往往面积大,盲目选最快的加法器会占用其他部件的面积,最后整体性能可能下降,这在工业上也有过案例。目前的商用CPU市场中,还没有一种完备的精确定价策略,目前定价所依据的是部件数量、晶体管数量这样的指标。

CPU在“速度与价格”上的进步(每代INTEL加速不加价),其实主要靠集成电路技术的发展,但这部分不是计算机系统的内容。那么,对于确定的指令系统层和集成电路技术,有如下几种提高速度的策略:

1) 缩短时钟周期:虽然这大部分都是集成电路方面的工作,但如果是通过改变逻辑电路的构造来降低数据通路的延迟,从而缩短时钟周期,那么这就属于微体系结构层优化。

2) 减少路径长度:执行一组操作所需的时钟周期数称为路径长度。比如有种想法是在PC寄存器增加独立的自增模块,减少ALU的使用次数。但是其效果可能不明显,例如MIC-1的Main1微指令是最常用的包含PC自增的指令,但是在Main1的一个周期里还包含内存fetch操作,省下PC自增操作也无法让Main1占用更少周期。又比如有种想法是让MIC-1中fetch的端口从8位改为16位,从而减少fetch次数。但这可能不能让fetch操作从2次降为1次,因为MIC-1的内存数据线(存储字长)是32位的,而MIC-1的操作数和操作码很多时候都是8位的,所以16位数据很可能是跨字的,这时还是需要2次fetch;

3) 指令重叠执行:可看作是种减少路径长度的方式,是设计人员最感兴趣,最有效的策略。比如说可以将PC、MBR、fetch控制信号整体作为取指模块独立出来,取指模块可以独立完成取操作码和操作数,而数据通路的其他部分可以同时执行其他的操作,这样就可能在同一时刻有两个指令在并行,实现明显的优化。对于更复杂的指令重叠设计,可以在同一时刻重叠更多个的操作;

MIC-1的结构十分精简,算上内存其晶体管数也不超过5000个。但这个结构已经能实现IJVM,所以接下来的任务就是一步步优化MIC-1的“速度与价格”。之后的文章会学习更复杂的方案。

合并主循环与微指令

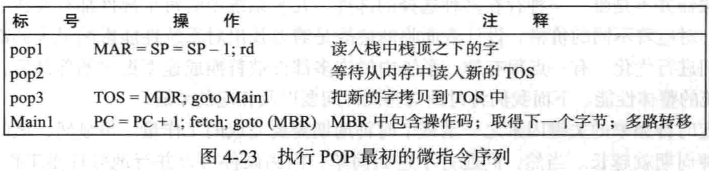

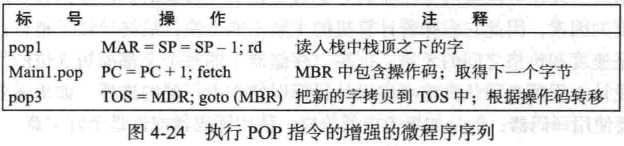

之前给出过用MIC-1实现所有IJVM指令的方案,该方案中的微程序是基于主循环结构的,指令是开始/结束于Main1的。比如上图第一张是POP指令结束后回到主循环(Main1)的例子。但想要实现“回到主循环”,并不代表一定要将Main1的所有操作都放在一个独立时钟周期(独立微指令)执行。比如上图第二张,其把Main1的操作分散并组合进原pop1~pop3里,实现了等价的逻辑,减少了1个时钟周期。

这就是第一种缩短MIC-1执行路径长度的方案,不过其不适用于大部分指令,因为Main1包含PC自增操作,该操作需要通过ALU,但一个时钟周期通常只能通过ALU一次。所以只能把PC自增操作合并到未使用ALU的微指令里,但大部分微指令都使用到了ALU。

这种方案是比较简单的,相当于“升级”实现IJVM的微程序,没有实体硬件的改动。

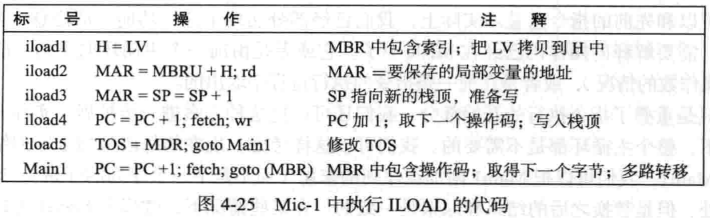

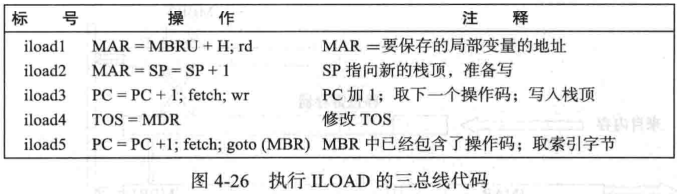

三总线的数据通路

MIC-1的数据通路包含B、C两条总线(内存总线不算),前者是ALU的右输入,后者是ALU的输出。这里考虑再为ALU的左输入再加上A总线。A总线的功能和B总线类似,可通过控制信号从大部分寄存器中选一个作为ALU的左输入。使用3条总线的一个优势是可在1个时钟周期里作任意2个寄存器的加法,比如上图第一张是MIC-1的ILOAD,其为了计算局部变量的起始地址+偏移量,需要先花费一个周期把起始地址LV存入H才能在下一个周期做加法。如果使用了A总线那么就能直接做加法,从而节省一个周期。