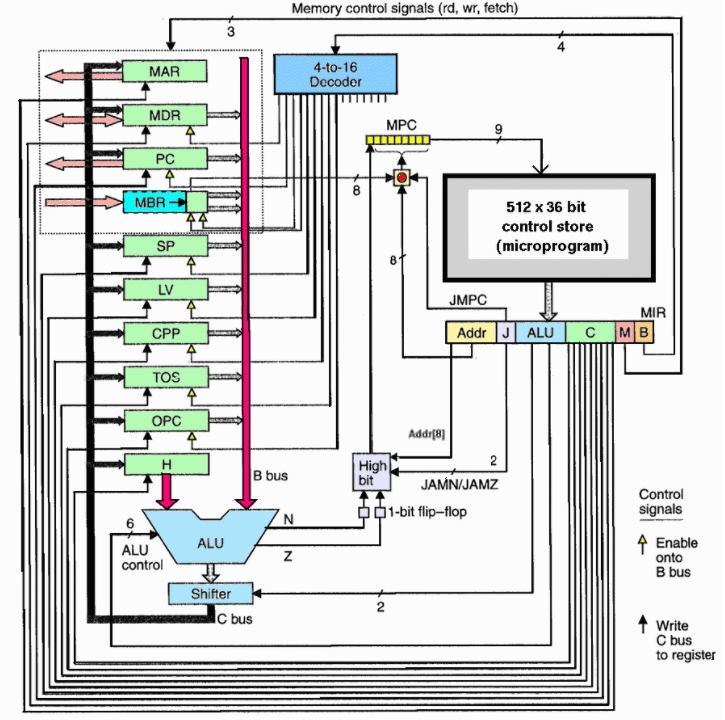

MIC-1的组成

完整的MIC-1微体系结构如上图所示,其由数据通路和控制部分组成。这里需要说明一下控制部分所引入的部件,以及之前没讨论到的一部分数据通路上的信号:

1) 控制存储器:计做CS,图中512*36位的只读存储器,是控制部分最重要的电路,其固化了用于实现ISA指令的所有微指令,其至多能存储512条微指令,其功能和只读内存相似,其中的每条微指令都有自己的地址,微指令的地址也叫微地址。该CS接受的输入是微地址,输出是微指令。由于实现指令系统类似于在CS中写程序(填微指令),所以也把整个CS中的微地址和微指令统一称为微程序;

2) 微程序计数器:图中MPC,功能类似MAR,是微地址的寄存器;

3) 微指令寄存器:图中MIR,存储将要执行的微指令。上图MIR画的很像微指令;

4) N与Z连接的方框:两个1位触发器,其数据写入时机和“内存写入寄存器”、“C总线写入寄存器”一样,也是时钟上升沿的边沿触发;

5) “O”方框:组合逻辑。若JMPC=1输出ADDR(低8位)和MBR的按位或,JMPC=0输出ADDR(低8位);

6) “High Bit”方框:组合逻辑。输出“(JAMZ 且 Z) 或 (JAMN 且 N) 或 (ADDR最高位)”;

7) “4-to-16 Decoder”:前面提到过的用于减少信号位的4-16译码器;

内存中的ISA指令通常是顺序执行的(没有遇到跳转指令时),而控制存储器中的微指令不是顺序着地址执行的,下一步要执行那一条微指令取决于当前微指令的ADDR和J,以及数据通路中的MBR和ALU的N、Z。它们共同决定了下一个微指令的微地址。

MIC-1的时序逻辑

这里分析MIC-1微体系结构是怎么在时钟下执行微指令的,其各子周期如下:

1) 在每个时钟周期开始前,MPC已准备好微地址,CS已稳定输出根据MPC找到的微指令;

2) 时钟开始(下降沿到达),微指令打入MIR,过一段时间MIR输出稳定;

3) 微指令对应的36位信号稳定,4-16译码器选择的寄存器把数据送上B总线,然后B总线有稳定输出。而ALU与移位器的控制信号同样早已稳定。C总线的写入控制信号也早已稳定,但寄存器的写入需上升沿触发,所本子周期内不会有C总线到寄存器的写入、内存总线到寄存器的写入。ADDR和J会影响到MPC,但之后MPC会恢复正确。本子周期确定了ALU的输入和控制信号,且保证这些信号都已稳定;

4) 经过一段时间,ALU和移位器能够稳定输出正确结果(包括N和Z),进而C总线的输出稳定;

5) 上升沿到达,微指令的部分控制信号实际在该子周期才实际有效。C总线的输出会被“打入”1个或多个寄存器。之前的内存操作(如果有)返回的数据被“打入”寄存器MDR/MBR(注意不能和C总线写入的寄存器一样)。N和Z上的触发器也会被“打入”当前的N和Z;

注意在(5)中不排除寄存器H被打入数据造成ALU输入的变化,以及进而引起的ALU输出、N、Z的变化!但前面提过时序被严格控制,所以H改变造成的N,Z改变在“打入”结束时过一会儿才会被输出,即N,Z对应的触发器被“打入”的数据是(4)阶段对应的N,Z的输出。另外可发现用N,Z信号+触发器就是为了避免这种情况,直接用ALU的输出来控制会出问题,寄存整个ALU的输出那代价又太大(元件太多)。

6) 经过一段时间,寄存器输出稳定,N和Z的触发器输出稳定,进而“O”和“High Bit”方框的输出稳定。另外如果有内存总线上有控制信号,内存会在该阶段根据内存地址线、内存控制线执行内存操作;

7) 经过一段时间,MPC稳定输出新的微地址,下个周期即将开始,即回到(1);

注意在(7)中MPC和其他寄存器显得不同,其不是上升沿边沿触发的,其可以是高电平水平触发的,也可以是让上升沿接入延迟后再边沿触发的。更本质来看,MPC更应该是“导线”而非寄存器。因为MPC的输入端在(6)之后直到下个时钟周期都会保持正确,所以没有必要再加一道寄存器(面积是宝贵的资源),直接把输入转接给CS即可。这种情况下也称MPC为虚拟寄存器。

MIC-1的微指令的跳转

这里具体看一下MIC-1的微指令跳转的逻辑。这里分情况来看:

1) JMPC=JAMN=JAMZ=0:最简单的情况,下个地址等于当前微指令的ADDR;

2) JMPC=0,JAMN或JAMZ=1:用上面的“High Bit”的定义式计算可知,下个地址等于当前微指令的ADDR或“最高位改为1的ADDR”;

3) JMPC=1:这时就需要跟发生内存交互。注意到这里我们还没有在CS里“编写整个微程序体系”,因为还不知道IJVM具体指令的情况。这里只能说JMPC=1时当前微指令的ADDR是000000000(0x000)或100000000(0x100)。由于我们设计微体系结构确定了MBR只有8位,所以对于一个确定的ADDR(0x000或0x100),在JMPC=1时新ADDR可能会是16*16=256种结果中的一种。一种典型用法是这样,MBR只包含ISA指令中的操作码,这样使用JMPC=1就能得到对应于这个ISA指令的微地址(微指令)。