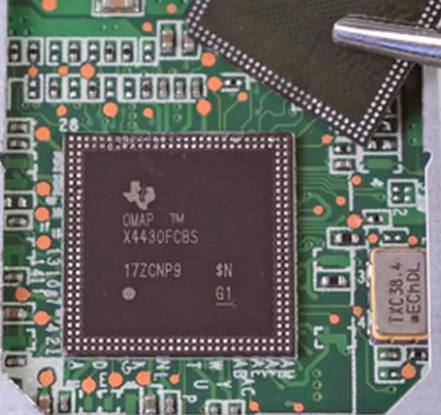

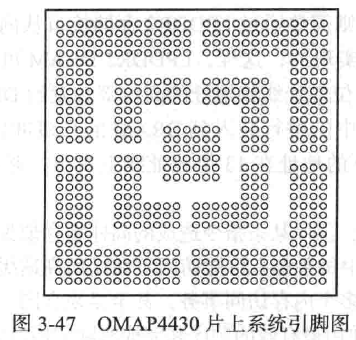

OMAP4430片上系统

OMAP4430是德州仪器2011年的产品,基于德州仪器第4代OMAP(开放式多媒体应用平台)架构。使用OMAP4430片上系统的代表产品有LG Optimus 3D、Motorola Milestone 3、Motorola Atrix等。这款芯片是一个片上系统(SoC),所谓SoC就是指芯片中不仅包含CPU的部分,还可能包含GPU、手机通信基带等等。目前SoC和CPU之间的区别越来越小,比如INTEL的CPU需要和主板上的INTEL芯片组一起工作,在之前INTEL主板有北桥芯片和南桥芯片,后来北桥芯片就装进了CPU内,主板上就只剩下了南桥芯片,也就是说后来的INTEL处理器也可看作SoC。

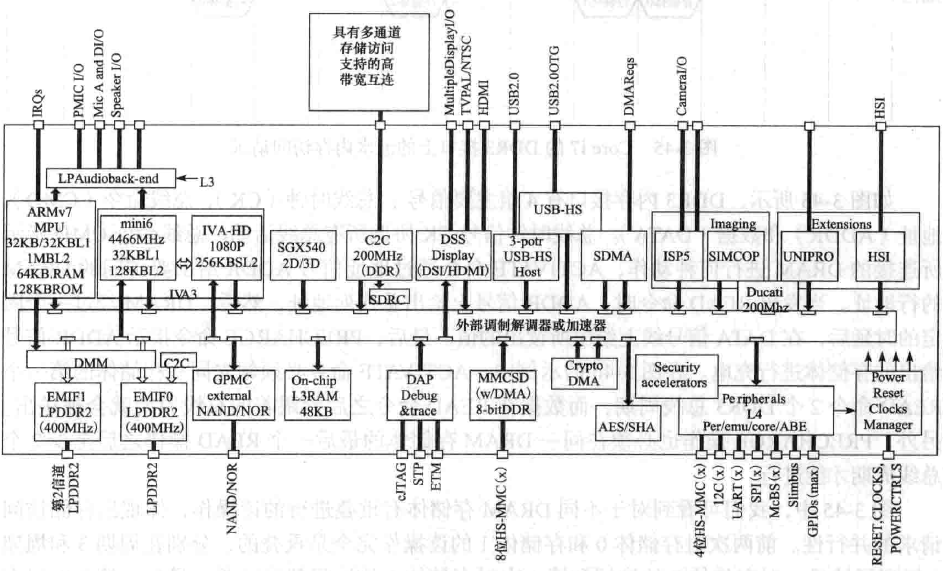

内部结构

OMAP4430和酷睿的最大区别是其使用ARM指令集,其应用场景不在PC/笔记本,在高性能的移动/嵌入式场景,比如智能手机、平板、物联网设备等。这里来看OMAP4430内部的模块:

1) CPU:2个ARM Cortex-A9处理器(核心),ARM Cortex-A9核心具有2发射超标量的微体系结构,指令集为ARM v7,主频为1GHz,流片工艺为45nm;

2) 加速处理器:加速处理器是指专门用于特定场景的处理器,当遇到这部分场景时加速处理器会替代CPU来完成计算任务。OMAP4430中重要的3个加速处理器为图形处理器(GPU) POWERVR SGX540、图像信号处理器(ISP)、视频信号处理器IVA3;

3) 外部设备接口:比如触摸屏、键盘控制器、DRAM、Flash、USB、HDMI等等;

OMAP4430将其各个处理器部件精心设计调试为低能耗的,在满负载下其功耗为600mW,仅为酷睿等PC端CPU的百分之一的量级。并且其引入了这样两种能量管理方法:

1) 动态电压调节(DVS):即OMAP4430上的某个部件不满载时,适当降低其电压。这种技术也用于更新的酷睿处理,当CPU不满载时,会适当降低其电压和频率,称为动态电压频率调节(DVFS);

2) 门控电源:即OMAP4430上的某个部件在不被使用时,可以暂时断开其供电;

除了节省能耗,OMAP4430的ARM A9核心是非常高效的,其可在每个周期译码和执行至多2条ISA指令,这代表了其最大吞吐率。不过由于指令不一定都能够“并行”,故大多情况下不能有这么高的吞吐率。为此ARM设计了强有力的分支预测、乱序执行等,并对存储系统做了高度优化。

高速缓存与LPDDR2内存操作

OMAP4430上的每个ARM A9核心都有核心私有的2个L1高速缓存,1个32KB的指令缓存,1个是32KB的数据缓存。其和酷睿一样具有L2高速缓存,不过OMAP4430的L2高速缓存由2个ARM A9核心共享,并且仅有1MB。OMAP4430支持LPDDR2内存,其高速缓存由LPDDR2内存提供数据。LPDDR2标准由DDR2标准改进而来,LPDDR2适用于低能耗场景,并且使用更少的导线。另外LPDDR2的存储控制器还支持预取、预处理的技术。OMAP4430的LPDDR2接口是集成在SoC内的,LPDDR2内存可以直接连接OMAP4430,并且OMAP4430有两个LPDDR2接口,即支持双通道内存,两个通道(总线)可以并行的访问。

这里非常简单的讨论下OMAP4430的高速缓存操作,缓存的基本单位是缓存行(Cache Line),CPU在处理缓存方面的东西时会将内存“按缓存行编址”,OMAP4430中1个缓存行=32字节。其在工作时会将访问次数最多的1024个数据行和1024个地址行放入L1缓存,L2缓存保存访问次数相对少的数据行和地址行。当在L1缓存没有找到所需的行时,CPU会将行的标记地址发送给L2,问L2有没有这个行,如果L2里有,CPU需要花费19个周期获得这个行,代价比较大。如果还没找到会去LPDDR2内存找,代价更大。

然后非常简单的讨论下OMAP4430的内存操作,在进行内存访问时,OMAP4430首先将地址的高位放到13位地址线,执行ACTIVATE(跟之前讨论的DDR3类似,用于激活内存行),然后内存会把整个行(内存行不是缓存行)的数据装入行缓冲区。然后继续在控制线发出多个读或写的操作,同时把地址的低位放到13位地址线上,并在32位的数据线上发送接收数据(也是32位)。

由于内存操作需要的周期很多,CPU会用这些周期做别的事情,做别的事情可能又需要内存操作。所以OMAP4430的两个LPDDR2内存总线会并行的工作,甚至处理来自同一个CPU的任务。通常对内存的操作都会采用突发读写,因为从内存读到的数据往往要存入高速缓存,而高速缓存的行会比字长要长。