接口电路

接口电路是指计算机之间,计算机与外围设备之间,计算机内部部件之间起连接作用的电路。一般由寄存器组、专用存储器和控制电路几部分组成,当前的控制指令、通信数据、以及外部设备的状态信息等分别存放在专用存储器或寄存器组中。

接口电路这4个字容易令人望文生义,联想到PCIe接口、USB接口。实际上接口电路一定程度上与总线这个概念平行,并且有部分的重合。接口电路强调两个部件直连,总线强调多个部件用公共的总线互连。接口电路强调信号和数据形式的转换,总线更注重可扩展性、灵活性、规范化。接口与总线有时也不加区分,合称为总线接口。通常接口电路是连入计算机系统总线的,比如INTEL 8255A接口电路芯片。

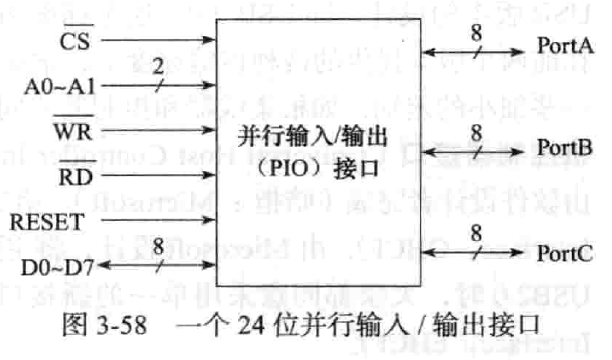

上图是个类似INTEL 8255A的接口电路芯片引脚图,是种并行IO接口(PIO)芯片。右边3×8根IO信号线可用于连接各种支持它的IO设备,可以是键盘,开关等。左边包括接入总线的D0-D7信号线,WR/WD的写信号线/读信号线,RESET充值信号线,A0-A1的地址信号线,CS片选信号线。该PIO接口芯片可通过3位的配置寄存器配置,来设置3个Port的输入输出,而每个Port都会对应一个8位锁存器用来暂存数据。

地址译码电路

讨论完IO接口电路后,我们发现可以有这样的计算机系统,其地址总线同时接入了内存和IO接口电路这两个设备。这时就需要借助地址译码电路和两个设备上的片选信号线,实现访问正确设备上的正确地址。地址译码电路的思路类似于定位内存地址的电路,不同的是IO接口通常仅需要很少的几个地址,这使得地址译码电路和内存地址电路是有区别的。事实上在PCI总线规范中,IO接口接入PCI总线时,可选择接入IO地址空间或内存地址空间,后一种方式也称为内存映射IO(MMIO)。

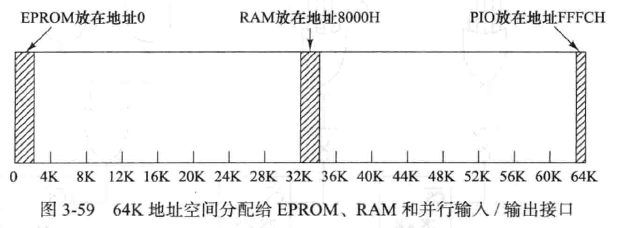

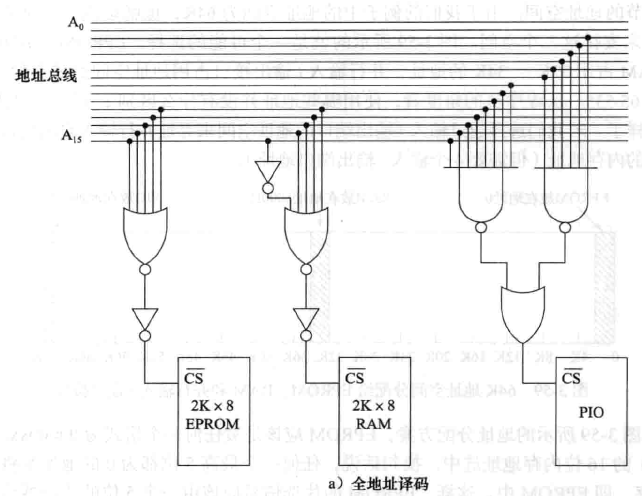

这里构造一个简单的计算机系统来研究两种地址译码电路,其由一个CPU,一个存放程序的2K个8字的EPROM,一个作为内存的2K个8字节的RAM,以及一个上述的PIO芯片组成,他们共享64K的地址空间,并且按EPROM占用0-2K,RAM占用32-34K,PIO芯片占用65532-65535的方式分配地址,这种分配方式能够简化地址译码电路的设计难度。

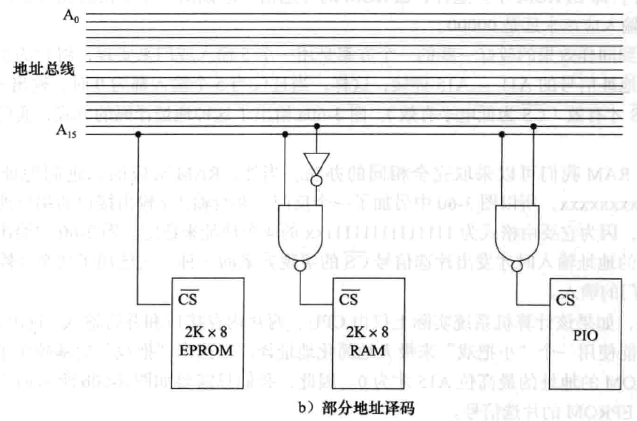

上图(a)称为全地址译码,只有当地址绝对符合设备地址范围时,片选信号才能为0(0为有效)。而上图(b)称为部分地址译码,因为无效地址可能同样会让某设备的片选信号为0,不过这是安全的,因为即使片选有效,这些设备也没有用到这些地址。但是如果要考虑系统未来的扩展(在地址总线加入更多设备),那么部分地址译码应该尽量避免,因为其划分地址空间的粒度太大,会浪费地址空间。

除了上述两种地址译码方案外,还有第三种常用的方案。其把地址线的高3位接入3-8译码器,这样就能得到8个输出信号,刚好8个输出信号能用于划分出第1个8K地址空间、第2个…共8x8K。然后把第1个输出信号,第5个输出信号,第8个输出信号分别处理为EPROM、RAM、PIO的片选信号即可。这等于是一种加入了3-8译码器的部分地址译码。