PCIe总线

随着技术发展,PCI的带宽已成为新IO设备的瓶颈,且PCI总线的插槽设计的也不是很合理,所以人们试着提出新总线标准。目前在主流PC、服务器中,占据统治地位的PCI总线的继任者是PCIe总线,全称为PCI Express总线。这种总线标准也是Intel提出的,其实际上和PCI总线几乎没有关系。可能Intel是因为考虑到PCI这几个字母已经成为了“品牌”,所以打算在名称上继续沿用它。

PCIe的核心在于它彻底抛弃了作为“连接众多设备的并行公共导线”的传统总线功能,取而代之的是提供基于“高速点对点串行连接设备”的总线功能。这就是为什么说PCIe和PCI是完全不同的,PCIE从局域网、交换以太网中借鉴了许多重要的思想,这使得PCIe非常的强大。

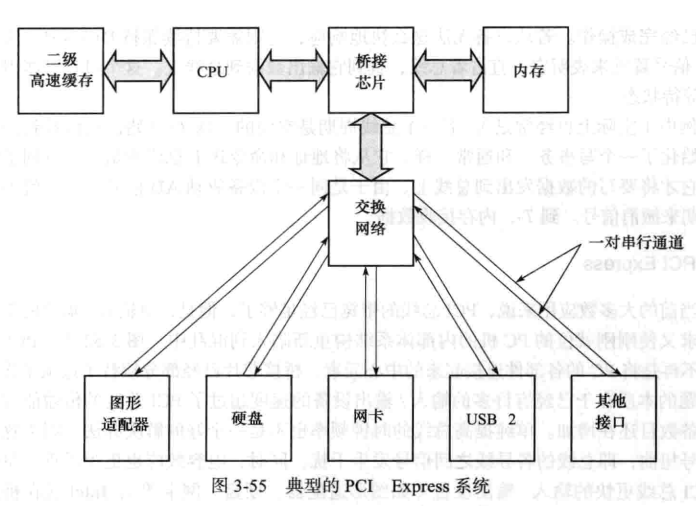

Intel在中后期版本的Intel奔腾4对应的主板上开始提供PCIe总线,上图提供了1种包含PCIe总线的计算机结构。其中CPU与内存仍采用原方式连接,IO设备则是经过PCIe所提供的交换网络与桥接芯片通信的,这里的交换网络是个逻辑概念,因为其功能通常被内置到CPU或桥接芯片中。

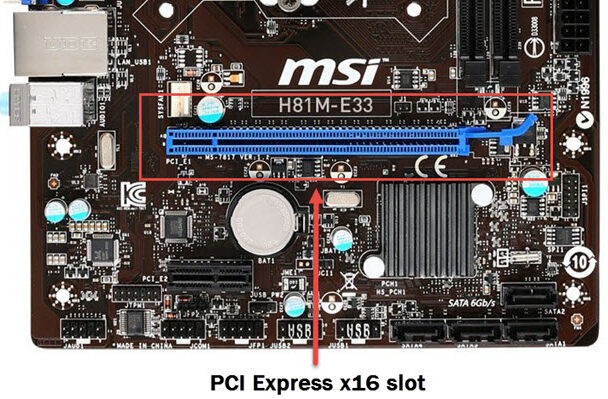

在上图的结构中,每个IO设备与交换网络间都只有1个PCIe数据通路(lane)。每个PCIe数据通路又包含2个单向传输通道,分别用于“交换网络-设备”和“设备-交换网络”。而每个通道又会包含两个物理导线,一个传输信号,一个接地(用于更好的抵抗干扰)。平时更习惯把PCIe数据通路称为PCIe通道,主板说明书中描述PCIe插槽的“PCIe x16”表示该插槽包含16个PCIe数据通路,在PCIe总线下,可以用相对于PCI更统一的方式处理不同接入设备,PCIe与PCI有具体这样几点关键区别:

1) PCI设备类似于“并联”在一起(类似于共用导线),设备发出的信号对其他设备都可见,但设备们都只处理与自己有关的信号,这类似于网络广播。而PCIe设备则是点对点的;

2) PCI是并行传输的,PCIe是串行传输的;

3) PCI在工作时(譬如读内存)是主设备并行发出多种信号,然后并行(32条AD线同时并行的传输)的逐个读取字。PCIe则是一个设备发数据包给另一设备,这里的数据包非常类似计算机网络定义的数据包,其可分为包头和有效载荷,其中包头含控制信息,作用类似于PCI总线中的控制信号,而有效载荷则类似PCI数据信号。这类似于包交换网路;

4) PCI只提供1位的纠错检错信号(码),而PCIe提供更强大的纠错检错能力;

5) PCI要避免并行数据因导线布线等造成的延迟破坏时钟同步,不能轻易缩短时钟周期和延长导线。而PCIe则可极大缩短时钟周期且设备与交换网络的距离(导线长度)可达50cm;

6) PCI不在硬件层支持热插拔,而PCIe有用于处理热插拔的“信号”;

7) PCI通过在总线接入PCI桥扩展,而PCIe通过在交换网络接入新交换网络扩展;

8) PCI插槽体积大,而PCIe插槽可以做的比较小;

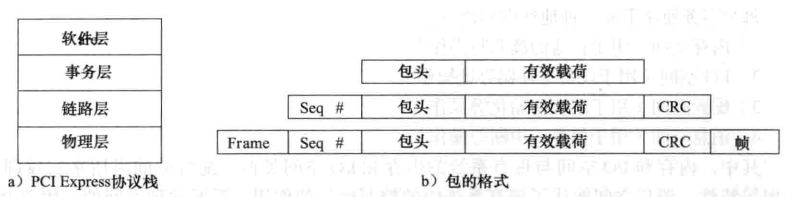

PCIe协议栈

由于PCIe总线的通信与计算机网络相似,所以PCIe总线也对应有类似于网络的OSI分层模型,该模型有4层,每层都包含若干子协议。它们共同构成上图的协议栈结构,具有4层协议栈的PCIe总线有远超“公共导线”的能力。这4层的功能大致如下:

1) 物理层:实现发送设备和接受设备间的数据位的传输;

2) 链路层:实现由多个位组成的数据包的传输;

3) 事务层:用于处理事务,比如从内存读1个字需2个事务,分别由CPU、内存发起;

4) 软件层:该层次就是操作系统可见的PCIe的“接口”,操作系统、驱动程序可以在此控制PCIe总线系统,并做进一步的封装,从而提供更高级的服务;

PCIe物理层

物理层主要解决位传输的问题。在前面图片中,每个IO设备与PCIe交换网络间只有1个信道(数据通路),每个信道由1对单工(单向传输)连接构成。而对于实际使用中的一般情况,两点间通常会有2、4、8、16、32个信道。PCIe总线与PCI总线不同,其在物理层没有直接使用时钟信号,设备在需要传输时会立即串行传输比特位。这种方式相比于PCI的同步传输会给人带来一些困惑,比如说“在没有时钟时,如发送方连续发出多个二进制0,接受方如何知道具体发送了多少个0”。

PCIe通过各种复杂机制来解决这个问题,首先是引入8b/10b编码,其按8位为一组得到10位的编码,这种编码可以保证编码后的数据流中,每5个比特内有一次01的转化,不会连续出现大量的0或1。于是数据流中就会有足够的电平变化频率,进而接收端可通过锁相环从数据流“反推”出时钟,这称为时钟恢复(CDR)技术,相当于发送端把时钟信息“嵌入”到了数据流中,而接收端可以从中“提取”出时钟。时钟恢复技术使串行总线具有了可行性,从而实现远高于同步并行总线的效率。

PCIe链路层

链路层主要解决数据包传输问题。链路层得到事务层数据包后,会在数据包附加序号和CRC校验码,接收方收到包后,会计算CRC并和数据包附带的CRC比对,若两CRC相同,接收方的链路层会回复确认包(ACK)表示该包已经正确送达,否则接收方会请求重新发送该数据包,相应的发送方链路层会将位于重放缓冲区的该包重新发送,即具有重传机制。另外链路层具有流量控制机制,接收方会在初始化时向发送方报告自己有多少空间缓冲到达包,当这些空间用完后,发送方应当停止发送数据包,直到接收方报告自己当前具有足够的空间。

PCIe事务层

事务层主要用于处理更粗粒度的称为事务的东西,比如“从内存读一个字”的功能通常会拆分成2个事务:

1) 由CPU或DMA通道发起的数据访问请求事务;

2) 由提供数据的从设备发起的事务;

PCIe事务使用的地址不是统一编址而是独立编址的。每个PCIe事务使用如下地址空间之一:

1) 内存空间:用于内存地址的访问;

2) IO空间:用于外设等设备的寄存器的地址;

3) 配置空间:用于初始化操作,支持PCIe热插拔的特性;

4) 消息空间:用于信号、中断等操作;

另外事务层还能够在数据包的基础上提供更高级服务,比如将1个信道拆分成多个虚电路,用于传输不同类型的数据流。事务层还会为不同类型的数据包加“标签”,比如“高优先级”、“可乱序发送”等。

PCIe软件层

软件层提供了操作系统与PCIe系统的接口。PCIe软件层对PCI总线兼容,即仅支持PCI总线的操作系统可在不修改代码的情况下直接使用PCIe总线。当然,对于新版本的操作系统,为了能够全面发挥PCIe总线的能力,会针对PCIe总线的特性修改代码。