Intel酷睿i7处理器(第二代)

第二代(Sandy Bridge)酷睿i7采用了32nm工艺,主频可达3.5GHz,是8086/8088后裔中比较年轻的一员。Intel为第二代酷睿i7提供了很好的向前兼容性,其具有和前辈80386、8048以及Pentium家族相同的指令系统层,包括相同的寄存器数目、指令集、浮点数标准等等。并且虽然它的性能与晶体管数远远超过了最前辈的8088处理器,但它还是向前兼容了8088,也就是说第二代酷睿i7可以不加修改的运行8088程序。当然第二代酷睿i7也包含了很多新的特性,比如新的加密指令等等。

第二代酷睿根据价位分为2-6核的版本,对于使用这种CPU的计算机,从计算机系统的角度应把它当成是多CPU的。程序员可利用多CPU优势编写多线程程序,通过真正的并行来提升速度。Intel在早期的Xeon服务器CPU中使用了超线程技术,超线程同样用在了第二代酷睿i7中,该技术可在1个物理CPU核心上创建2个硬件级的逻辑线程,简单来说就是在硬件层用1个物理CPU虚拟出多个CPU,所以带有超线程技术的CPU在操作系统的“硬件资源管理器”中会显示更多的CPU数。第二代酷睿i7有优秀的微体系结构层设计,支持同时执行4条指令,使之成为4发射超标量计算机。

第二代酷睿i7中包含3层Cache(最新代的酷睿i7也还是3层Cache的),其可按到核心的“距离”可分为一级缓存L1、二级缓存L2、三级缓存L3。其中每个核心有独享的32KB数据L1、32KB指令L1、256KB的L2。而L3则根据核心数为4~15MB。这种3层Cache的设计极大提高了内存性能,但是也占用了芯片面积。由于存在核心独享的Cache,第二代酷睿i7需要有机制既保证“Cache-内存一致性”又保证“多核间Cache一致性”。

第二代酷睿i7使用了2条主要的系统总线,其都属于同步总线。一条是用于访问DDR3内存的DDR3内存总线,另一条是用于访问IO设备的PCIe总线。对于高端型号的第二代酷睿i7,还额外具有QPI端口,其用于连接多个CPU(这里就不是多核形式的多CPU,而是主板上有多个底座可以装入多个CPU产品),QPI的功能包括但不限于同步多CPU间的Cache,处理CPU间中断等多CPU管理消息。

第二代酷睿i7的能耗在17~150W,150W是个比较大的功率,很快就能耗尽笔记本电脑电池。为此其设计了5个等级的“睡眠状态”用于节能。CPU空闲时其会进入睡眠状态,空闲更长时间进入深度睡眠状态。睡眠时CPU只有“一部分”在工作,所以功耗大大降低。比如进入睡眠状态后,CPU只有Cache和中断处理可用,而进入深度睡眠后Cache会被清空并停止工作,寄存器的值则会被维持。

酷睿i7的时钟

之前时不时会提到CPU主频、CPU时钟信号的概念。这里不妨通过讨论第二代酷睿i7体系结构的时钟来澄清这些概念。事实上Intel很早就采用了“主频=倍频*外频”这样的“时钟框架”,并且一直沿用到今天。所以真正要澄清的是“主频=倍频*外频”这个“时钟框架”到底是什么。

Intel芯片组主板上有若干个晶振,这其中的XTAL会接入芯片组中的南桥芯片,而南桥中的时钟控制器会将XTAL输入转化为100MHz(大多数时候为100MHz)的时钟信号。这个时钟信号的频率被称为基频(BCLK)或外频。这里的“基”是指基础,因为这个时钟信号会作为该计算机系统中的一些其他时钟的基础。这里的“外”则是指在CPU外部,所以说CPU频率除了被称为主频也被称为内频。

然后就可以来看CPU主频是怎么来的了,事实上在从很早以前到现在Intel的CPU主频都不是靠内置电路提供的时钟,而是先把基频时钟接入CPU管脚,然后再通过CPU内置的倍频器把其频率提高数十倍,这样就会间接创建1个新的时钟信号,这个新时钟信号就会被作为CPU的主频。

对于这个体系的PCIe总线频率和内存频率,同样是直接采用基频或将基频做倍频得到的,它们的频率通常和主频通常都是不同的。

酷睿i7的管脚信号

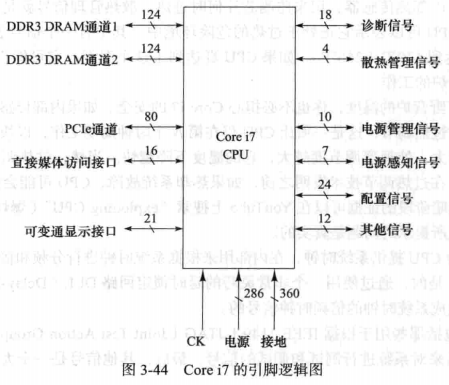

第二代酷睿i7包含1155个针脚,其中447个用于真正发送接收信号,286个连接电源(各种不同电压),360个接地,还有62个供未来使用。由于有些信号需要多个针脚,所以该CPU共有131种信号。上图给出了该CPU各种信号和功能,及其对应的针脚数。这里讨论一下其中的几种信号:

1) DDR3通道:该CPU具有2个DDR3通道,这2个通道上的内存可以并行工作。注意这里的通道数并非物理上的主板内存槽数,该CPU的实际主板可能会有2或4个内存槽,当有4个内存槽时,接入内存槽1,2通常等于把内存条接入通道1,接入内存槽3,4通常等于把内存条接入通道2。这也是为什么在组装电脑时会隔槽装内存,是为了能让2个内存条可以并行读写;

2) PCIe通道:PCIe是点对点串行传输的高级总线技术,PCIe通道中又包含多条“信道”,该CPU至多可以同时利用16个“信道”传输数据。支持不同“信道”数目的PCIe插槽的形状大小是不同的;

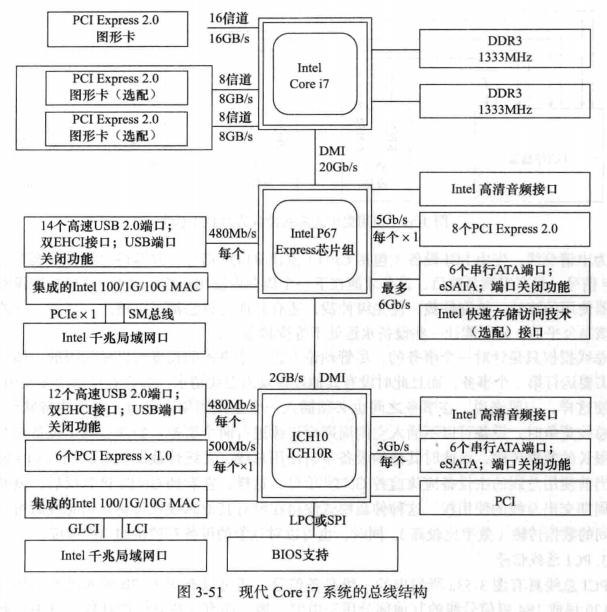

3) DMI接口(直接媒体访问接口):同于连接该CPU所配套的芯片组(在主板上)。该接口的速度大约是PCIe的一半。引入芯片组这样的结构可简化PC的生产制造。该CPU可配套如下2个芯片组成的芯片组:

3.1) P67:提供SATA、USB、PCIe等接口。PCIE除了“直连”CPU,还可通过芯片组连接;

3.2) ICH10:主要是兼容旧PCI、8259A中断控制等。其他功能有DMA控制器、实时日期时间等。这里的8259A是8088/8086中的中断控制器,这样该CPU就能够兼容8088的中断控制。不过通常来说该CPU会使用高级可编程中断控制器(APIC)这个新的中断控制器;

4) 电源管理信号:该CPU允许几档不同的工作电压,不过CPU不知道自己被电源加了多大电压,所以需要通过该信号告诉CPU电压。此外电源管理信号还会告诉CPU电源的稳定程度等信息。由于睡眠机制是为节点设计的,所以该信号也用于管理其睡眠状态;

5) 散热管理信号:该CPU内置了温度传感器,当CPU温度过高时,它会发出相应的散热管理信号,然后其他设备可能会协助其散热,比如CPU风扇转的更快。如果CPU的温度没有降下来还是越来越高的话,那么CPU会启用过热调节,这种方法让CPU仅在部分时钟周期工作,能迅速降低CPU温度;

6) 诊断信号:包括符合JTAG测试标准(IEEE 1194.1),用于对系统进行测试和调试的信号;

7) 时钟(CK):用于接入系统时钟(基频);

酷睿i7的DDR3内存总线操作

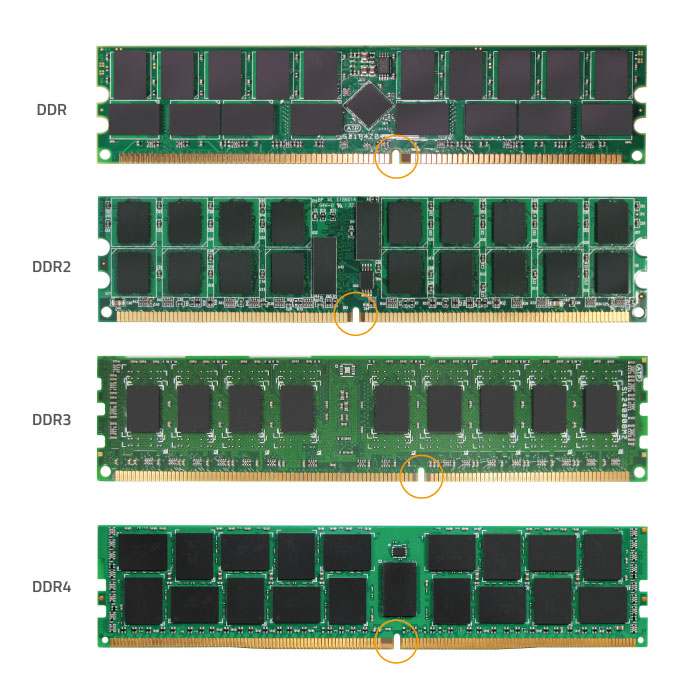

前面提到过DDR内存是直连CPU的,这是通过DDR内存总线(系统总线)与内存连接的。DDR内存总线提供了地址线、数据线、控制线。第二代酷睿i7支持的是第3代的DDR内存(DDR3内存)。

从物理的角度看,DDR3内存是内存条电路板,主板上可以接多个DDR3内存条,每个DDR3内存条上都有多个内存颗粒。对于不同DDR3内存条,其总容量、内存颗粒型号、内存颗粒数、颗粒宽度都不一定相同,常见的颗粒宽度有4位、8位。内存颗粒的内部可以看作是多个叠起来的平面,这个平面被称为逻辑BANK,每个逻辑BANK类似有行和列的大表格,其中每个单元格能存储1位。所以如果某个DDR3颗粒的颗粒宽度是8bit,那么其内部就叠了8层逻辑BANK。

从DDR3总线提供的操作的角度来看,每个DDR3通道(DDR3总线)中有多个BANK(物理BANK,之后会说其和颗粒、逻辑BANK的关系),每个BANK有行地址和列地址,如果制定了行地址和列地址,就能取出指定位置的64位数据,其将被一次性放入数据总线(DDR3标准规定数据总线的宽度也是64位)。

打通上述两个角度的是DDR3内存控制器,每个通道都有独立的内存控制器,其能将插在同通道的多个内存条上的多个颗粒进一步“叠在一起”,使通过行地址列地址足以取出64位数据,比如把8个8位的颗粒叠在一起,如果对他们发出相同的行地址和列地址信号,那么就能一次性操作64位的数据。所以这里就能够明确1个BANK=多个颗粒=多个逻辑BANK,并且其位宽=数据线宽度=64位。

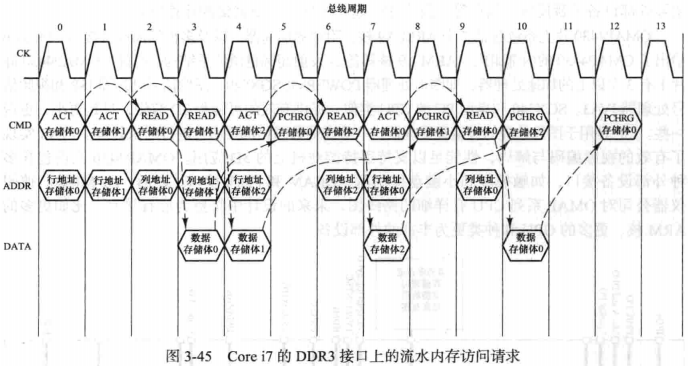

这看在某个DDR3通道(总线)上的DDR3内存操作示例:

1) 激活行:在控制线发出“激活行”,在地址线同时准备好“BANK序号(地址),行地址”。之后某个BANK的某行会进入激活状态。激活操作后需等待至少\(tRCD\)个时钟周期才能做读写操作,通常\(tRCD\)是定值并且是已知的。这里需要提到的是,1个BANK只能有1个行处于激活状态(3个BANK可以共有3个);

2) 读写:对当前已经激活的行进行读写。读写单个字(64位)时只需要在激活行后的周期,在数据线继续提供“列地址”。如果需要执行突发读写(操作连续多个64位的字),则需要在地址线同时提供“列地址”和“突发长度(字的数目)”。读写完成后如果之后不执行“预充电”,那么行的激活状态将一直被保持。可以在之后的周期继续对该激活行进行读写操作。内存收到读操作到内存把数据输出到数据线的时间间隔(时钟周期数)一般被计为\(CL\),这是评价DDR3性能的重要指标;

3) 预充电:把指定BANK的激活行变为“未激活行”。一个BANK在预充电操作后,需等待至少\(tRP\)个时钟周期才“关闭”之前该BANK的激活行,而其他BANK不受影响。这里\(tRP\)也是定值;

可以发现DDR3内存中,数据读写可能需要2~3个操作才能完成,并且这些操作会改变内存状态(激活行)。这个特点使DDR3内存的操作、状态、操作与状态的关系经常被用DDR3状态机描述。该特点也使得酷睿i7可对DDR3内存采用了流水线式的访问方式,这种访问方式能增加“并行程度”。考虑到该CPU本身是有2个独立的、可“并行”的DDR3通道,CPU与内存的速度差距会被大大降低。

上图是该CPU对1个DDR3通道的访问流程。CPU之所以“敢于”这样安排操作,是因为CPU是已经提前已经“知道”\(tRCD\)、\(tRP\)、\(CL\),等等整个流程所有活动的相关时序指标,这些指标提前就已经约定好了(类似于之前讨论过的同步总线下读内存字的过程)。