时序逻辑电路

组合逻辑电路中没有“时间”,其当前时刻输出仅取决于当前时刻输入。而时序逻辑电路的当前时刻输出不仅仅取决于当前时刻输入,还与电路之前的状态(输入输出)有关,其可继续分为这两大类:

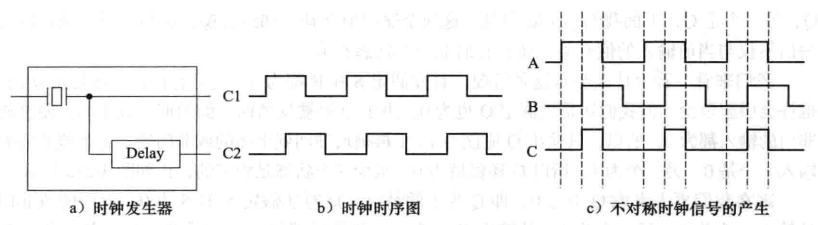

1) 同步时序逻辑:其特点是电路存在一个公共时钟信号,用于统一的控制协调各个单元的工作。时钟通常由晶振控制的,其会按固定时间间隔(计为\(t_1\))提供固定时间长度的脉冲(计为\(t_2\))。通常把\(t_1=t_2\)的时钟信号称为对称时钟,否则称为非对称时钟。有时为划分出更细粒度的时钟,会把时钟信号(\(C_1\))经过提供固定延迟的设备得到副时钟信号(\(C_2\))。这样在1个时间段里能区分出4个时间点,其分别为\(C_1\)上升、\(C_2\)上升、\(C_1\)下降、\(C_2\)下降。如果4个时间点不够,可继续增设更多得延迟时钟信号;

2) 异步时序逻辑:其特点是电路不存在单一公共时钟,各单元间不会按统一步调工作。比如下面要讨论的SR锁存器就是异步时序逻辑电路,因为其没有时钟也能工作(有点像组合逻辑);

SR锁存器

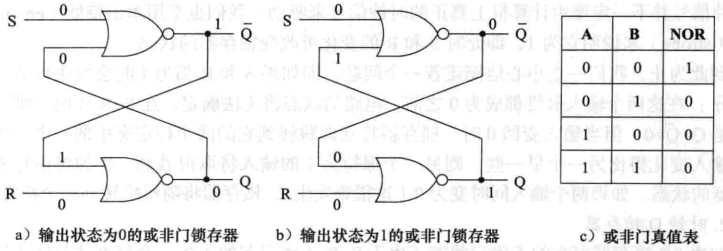

上面提到过在时序逻辑中,电路之前的状态可能影响到之后时间的状态,而SR锁存器就是具有这种性质的时序逻辑部件,其利用这个性质实现了1位的存储功能。SR锁存器的门电路如上图所示,其包含\(S,R\)两个输入,其中\(S\)用于设置锁存器,\(R\)用于重置锁存器。其包含\(Q\)与\(\bar{Q}\)两个互补输出。

SR锁存器相比之前讨论过的组合逻辑电路,有个非常不同的特性是或非门的输出是另一或非门的一个输入,也就是说SR锁存器种有反馈回路,这个回路使得SR锁存器在时序逻辑下实现存储。研究这种带反馈回路可以先枚举所有的输入情况,然后针对这些情况做具体分析:

1) \((S,R)=(0,1)\):继续枚举4种可能的输出如下:

1.1) \((Q,\bar{Q})=(1,1)\):可发现\(Q\)会被反馈机制调整为0,且接下来输出稳定在\((Q,\bar{Q})=(0,1)\)上,说明该输入下的输出不能稳定在\((Q,\bar{Q})=(1,1)\),会“跃变”到稳定的\((Q,\bar{Q})=(0,1)\);

1.2) \((Q,\bar{Q})=(0,0)\):同理\(\bar{Q}\)会被调整为1,“跃变”到稳定的\((Q,\bar{Q})=(0,1)\);

1.3) \((Q,\bar{Q})=(1,0)\):同理\(Q,\bar{Q}\)会被分别调整为0,1。“跃变”到稳定的\((Q,\bar{Q})=(0,1)\);

1.4) \((Q,\bar{Q})=(0,1)\):这时反馈机制不会调整,其是稳定的。综上这也是唯一的稳定输出;

2) \((S,R)=(1,0)\):根据电路的对称性其唯一的稳定输出是\((Q,\bar{Q})=(1,0)\);

3) \((S,R)=(1,1)\):利用上述思路分析其唯一的稳定输出是\((Q,\bar{Q})=(0,0)\);

4) \((S,R)=(0,0)\):利用上述思路分析可知有2种稳定输出,\((Q,\bar{Q})\)为\((0,1)\)或\((1,0)\)。输入稳定时,输出稳定为2者中的1种,且根据这种反馈的特性,其不会从1种跃变为另1种;

输入\((S,R)=(0,0)\)是较特殊的,其输出有2种稳定状态,输出究竟会是哪种取决于上阶段状态,所以这里不妨分析从1种状态变为另1种状态后的输出变化。这里先考虑只改变\(S\)或\(R\)的情况:

1) \((0,0)\rightarrow (0,1)\):由于\((0,1)\)只有1种稳定状态,所以转移后的输出同\((0,1)\)的输出;

2) \((1,1)\rightarrow (0,1)\):与(1)同理;

3) \((0,0)\rightarrow (1,0)\):与(1)同理;

4) \((1,1)\rightarrow (1,0)\):与(1)同理;

5) \((0,0)\leftarrow (0,1)\):分析反馈回路可知输出不变,刚好\((0,1)\)的输出也是\((0,0)\)的1种输出;

6) \((1,1)\leftarrow (0,1)\):与(1)同理;

7) \((0,0)\leftarrow (1,0)\):与(5)同理;

8) \((1,1)\leftarrow (1,0)\):与(1)同理;

这里分析下\((S,R)\)出现\((1,1)\rightarrow (0,0)\)的同时改变2个输入的情况。之前在组合逻辑的文章中提到过,实际电路中很难保证任意2个量能在同一时刻改变,所以输入\((1,1)\)可能是在短时间先变成\((0,1)\),然后再变成\((0,0)\),也可能是先\((1,0)\)后变成\((0,0)\)。这2种情况会导致\(Q\)最终稳定于2种不同的结果,且无法预知是哪1种。考虑到\((1,1)\)输入会带来这样的影响,并且其对SR锁存器的功能没有什么贡献,通常会规定任意时刻都不允许对SR锁存器输入\((S,R)= (1,1)\)。

组合逻辑中若存在竞争冒险,其输入稳定后输出就会正确。但时序逻辑单元SR锁存器不遵守这点,如果输入出现电压毛刺,SR锁存器很可能会稳定的输出错误的信息,其不会因为输入稳定而改变。比如上一阶段\((S,R)=(0,1)\),当前阶段\((S,R)=(0,0)\),如果当前阶段\(S\)突然有高电平毛刺导致\((S,R)=(1,0)\),那么其会“破坏”对上阶段的“记忆”,并稳定输出错误信息。

同步SR锁存器

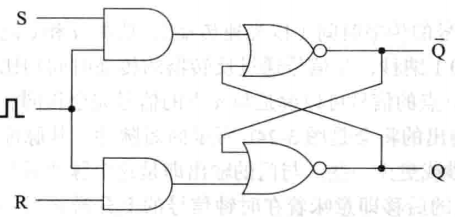

同步SR锁存器电路如上图所示,其除了具有\(S,R\)输入,还接受1个同步信号,只有同步信号保持在高电平时其\(S,R\)端才有等价于普通SR锁存器的作用。这是因为在同步信号为高电平时,\(S,R\)才能通过与门,而当同步信号为低电平时,两个与门只能都输出0,由于之前规定过不允许输入\((S,R)=(1,1)\),所以两个与门都只能输出0时不会影响到\(Q\)的状态。

可以发现只要保证同步信号电平下降时刻的\(S,R\)输入是正确的,那么\(S,R\)就能够进入锁存器中。不过为了“保险”起见,需要在该时刻前后的时间段保持输入的正确。

D锁存器

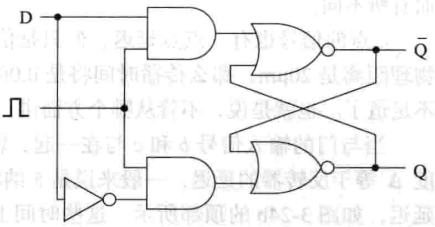

D锁存器电路如上图,是用\(D\)代替了\(S,R\)的时钟SR锁存器。D锁存器的功能相对比较明确,就是存储\(D\),分析可知在时钟信号高电平时的\(D\)会成为输出\(Q\),该过程可看作\(D\)被写入锁存器,当时钟信号电平下降后\(Q\)会维持同样的输出,这时可看作\(D\)被存储,只要不再一次对同步信号发出高电平,锁存器就不会被新的\(D\)影响,一直存储着之前的“数据”。D锁存器的功能就是1位寄存器/内存的功能。

可发现只要在同步信号电平下降前后的时间段,保持\(D\)的正确,那么其就会被存储。当然这个时间段应该稍微长一点点,因为新引入的非门会带来延迟。如果可以保证这一点的话,D锁存器还有个好处就是能从根本上杜绝\((S,R)=(1,1)\)的状态。

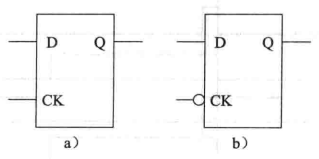

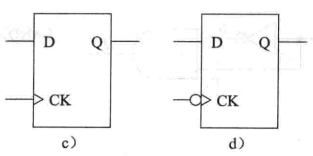

D锁存器实际上有多种实现,这里引入通用的D锁存器电路符号,其如上图。其中CK表示同步信号,图(a)表示的是和上述D锁存器功能一样的结构,而图(b)则表示同步信号反相的D锁存器。

D触发器

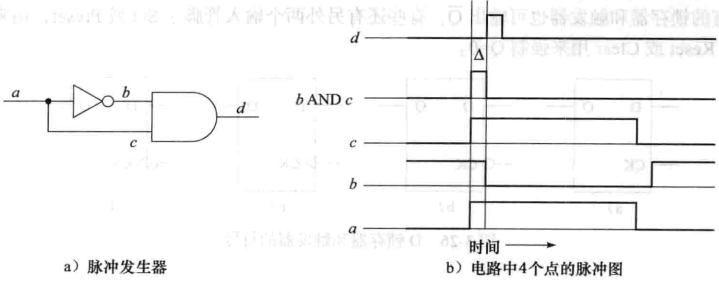

这里先来讨论上图中的脉冲发生器,其利用门相对导线的传输延迟在特定条件下形成脉冲信号,如果将其当作理想的逻辑电路则很难理解其原理,下面来分析其功能和原理,当\(a\)稳定在0时\(b,c\)显然稳定为\(1,0\),若此时\(a\)突变为1,则\(c\)会很快也变为1,但\(b\)会因为非门的延迟还要过一小段时间才会变成0,于是在这个短暂时间差里\((b,c) = (1,1)\),从而导致与门会短暂的输出高电平“毛刺”,然后继续稳定在低电平。这里再来看\(a\)从1突变为0的情况,同理在短暂的时间里\((b,c) = (0,0)\),这时就不会导致与门输出“毛刺”,因为其本来就稳定在低电平上。我们可这样归纳上述脉冲发生器的性质:“设\(t_1,t_2\)为其中的非门和与门的延迟时间,若\(a\)在\(t\)时刻电平上升,则\(t+t_2\)时刻\(d\)的电平上升,且高电平会继续保持\(t_1\)的时间”。更简而言之就是在同步信号上升沿发出短促的高电平脉冲。

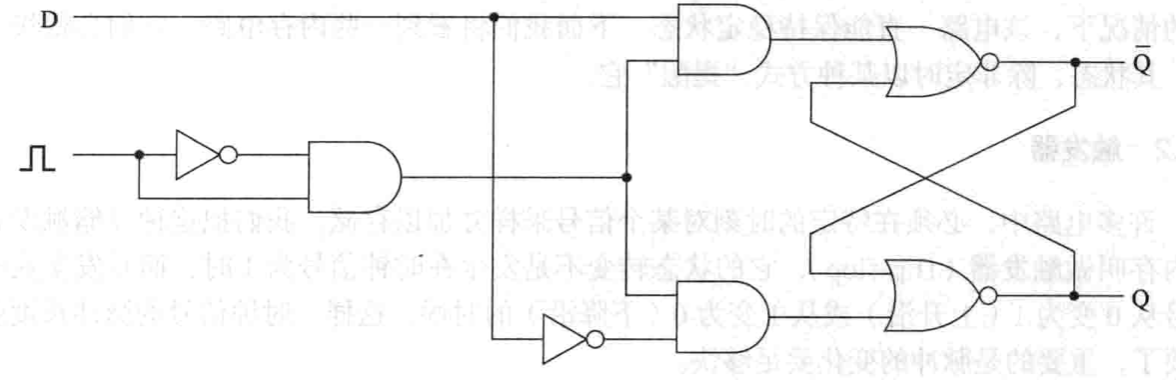

接下来分析D触发器的功能,其电路也在上图中,可发现其就是在同步信号前接入了脉冲发生器的D锁存器。其具体用法是先把“待写入数据”提供给\(D\),等待状态稳定后,通过1个脉冲完成写入。可发现其用法与D锁存器是有细小区别的,前者是在高电平的脉冲“时刻”发生的写入,后者是在高电平同步信号的时间段发生的写入。这两种方式分别称为边缘触发(边沿触发)与电平触发(水平触发)。D触发器会比D锁存器被更多的用于实现内存/寄存器,因为其边缘触发的方式会带来更好的稳定性。

D触发器实际上有多种实现,这里引入通用的D触发器电路符号,其如上图。其中CK表示同步信号,图(c)表示的是和上述D触发器功能一样的结构,而图(d)则表示同步信号反相的D触发器。

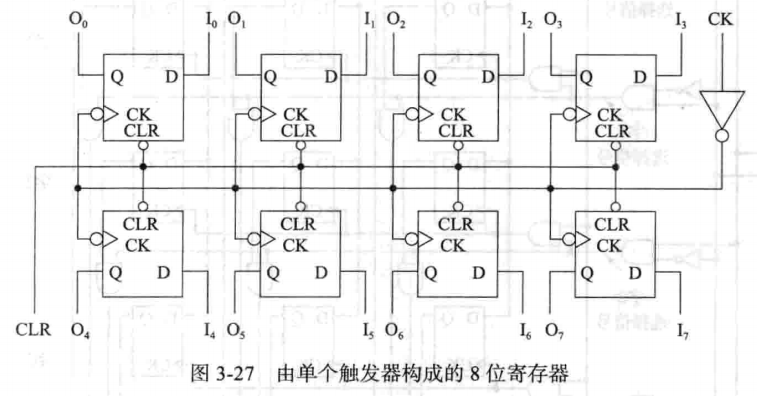

寄存器

寄存器通常由D触发器组成,上图是8个D触发器组成的8位寄存器,这里D触发器的同步信号是反相的,且有CLR输入。CLR用于清除触发器内容(存0),并联8个CLR得到的管脚可用于清除整个寄存器内容。注意同步信号CK在触发器外经1次反相,在触发器内又经1次反相,这是为了不改变电路逻辑的放大CK信号,因为公共的CK可能未提供足够的电流,这会进而使8个触发器无法“接收”同步信号,而在公共CK加入非门实际等于在电子技术层加入晶体管,晶体管有“放大”的作用。如果将这样的8位寄存器作为模块,并联多个模块的CK和CLR,就能得到16、32位寄存器,主流计算机的寄存器位数是字节的倍数。