组合逻辑电路(combinational logic circuit)

组合逻辑电路是指在任何时刻,输出状态只决定于该时刻各输入状态的组合,与其他时间的状态无关的电路。组合逻辑电路的功能可以用逻辑函数或真值表描述。接下来会讨论一些计算机内部经常用到的组合逻辑电路单元。

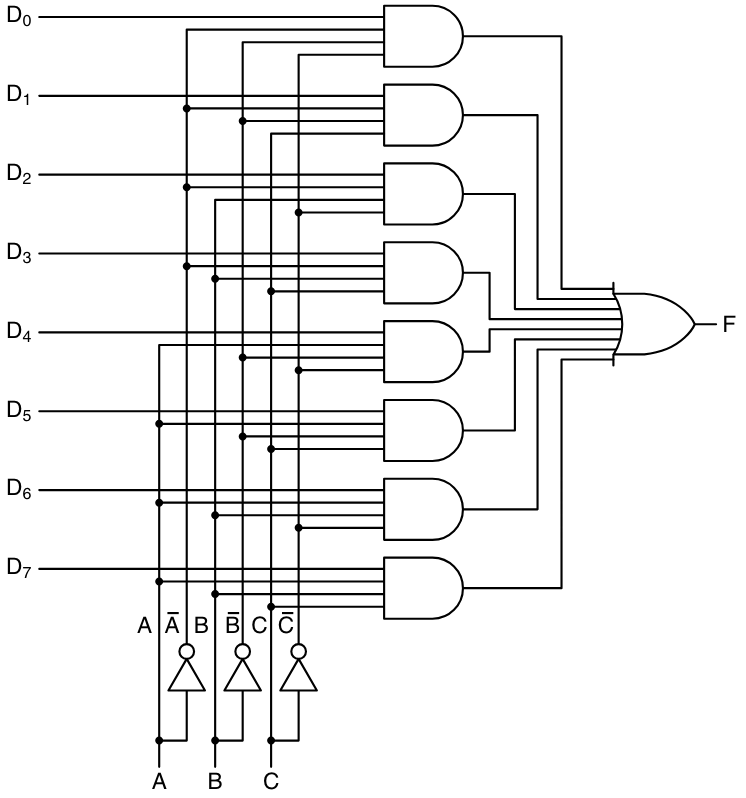

多路选择器(multiplexers)

上图就是1个多路选择器,其输入分为两部分,\(D_0\)~\(D_1\)是8个“待选择”的输入,而\(ABC\)则是提供“如何选择”的信息的。其功能是根据\(ABC\)状态的共\(2^3\)种组合,表示将8个“待选择”的输入中的哪一个送入后面的或门。当\(ABC\)的组合表示要选择某个\(D\)时,该\(D\)对应的与门收到的所有其他输入都是真,也就是该与门的输出会与其对应的输入\(D\)保持一致。而其他与门的输入将至少有1个为假。

多路选择器的一种应用是把并行信号转换成串行信号,假设并行的8路信号一直保持在多路选择器的输入端,如果ABC的信号依次变成其所有可能的组合,那么这8路信号的每一路会依次的称为或门的输出。

类似的还有多路输出选择器,其功能是根据控制信号,把仅有的单个输入发到某个输出。

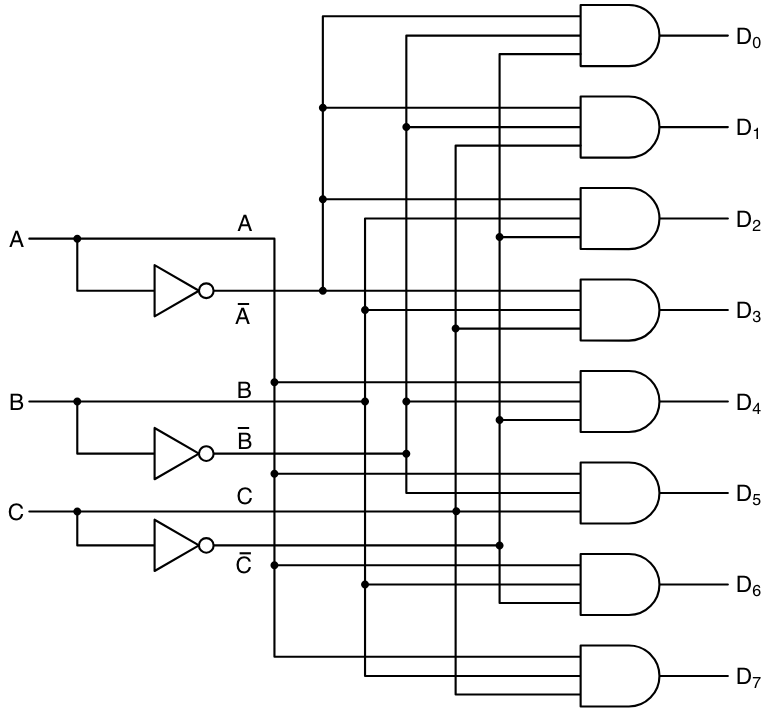

译码器(decoder)

上图是一个译码器,其通过ABC三者的状态的组合表示\(2^3\)种状态,8种状态一一对应于8种输出,每种状态表示将其对应的输出置1而将其他的输出置0。译码器可以用于“内存地址”的翻译,比如说内存地址的高3位是同来表示内存条上的8个存储芯片的,那么通过译码器就能找到对应的芯片,向其发出使能信号,让芯片进入工作状态。

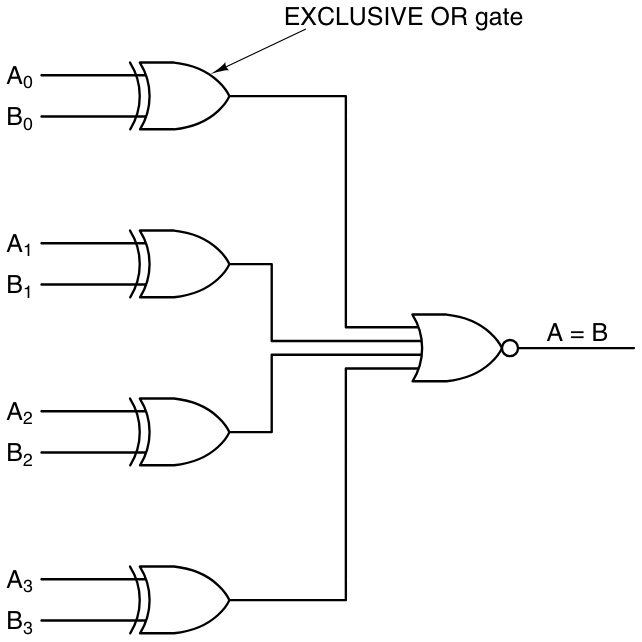

比较器

讨论比较器需新引入异或门这个基本单位,其符号如上图所示。异或门的真值表是两输入值相异则输出为1,否则为0。异或门可用前面提到的5种门构造出来。有了异或门后,比较器的作用就非常清楚了,上图所示的比较器的作用是当A,B的4个位完全相同时,则输出1,否则输出0。

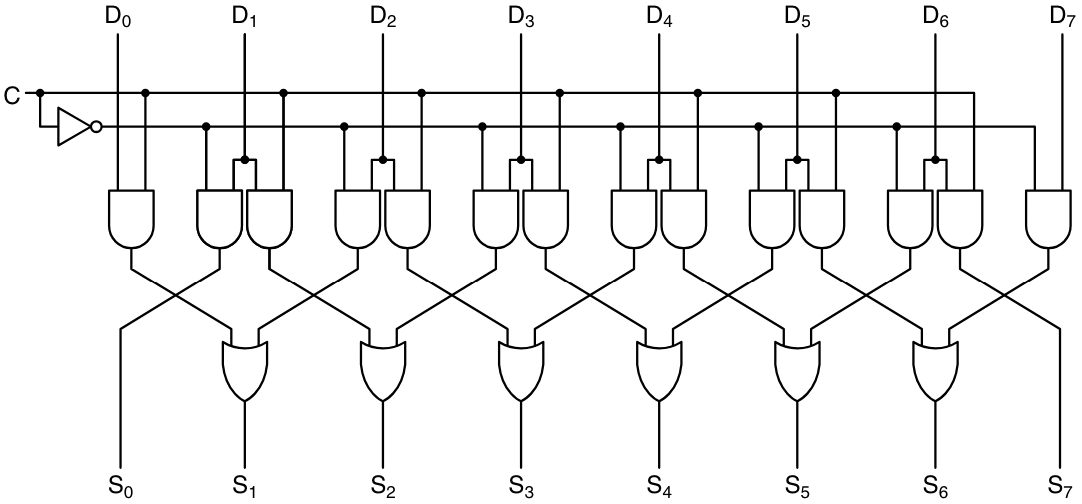

移位器

上述的8位移位器的功能是这样的,当控制信号C为0时,其会将输入左移,否则右移。其中8位数据的左移就是把输入的后7位左移,然后把最后一位置0。而右移则是把前七位右移,然后把第一位置0。这个电路其实很好理解,其使用了与门和或门。

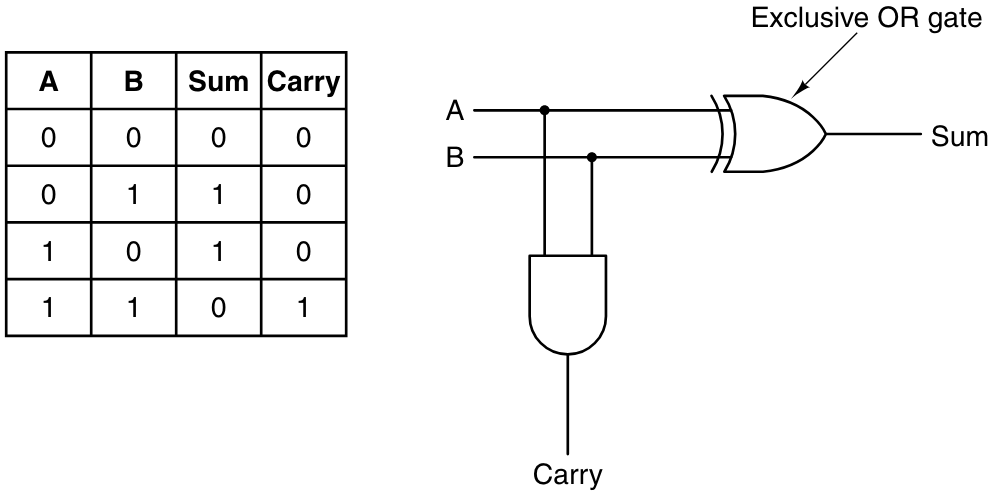

半加器

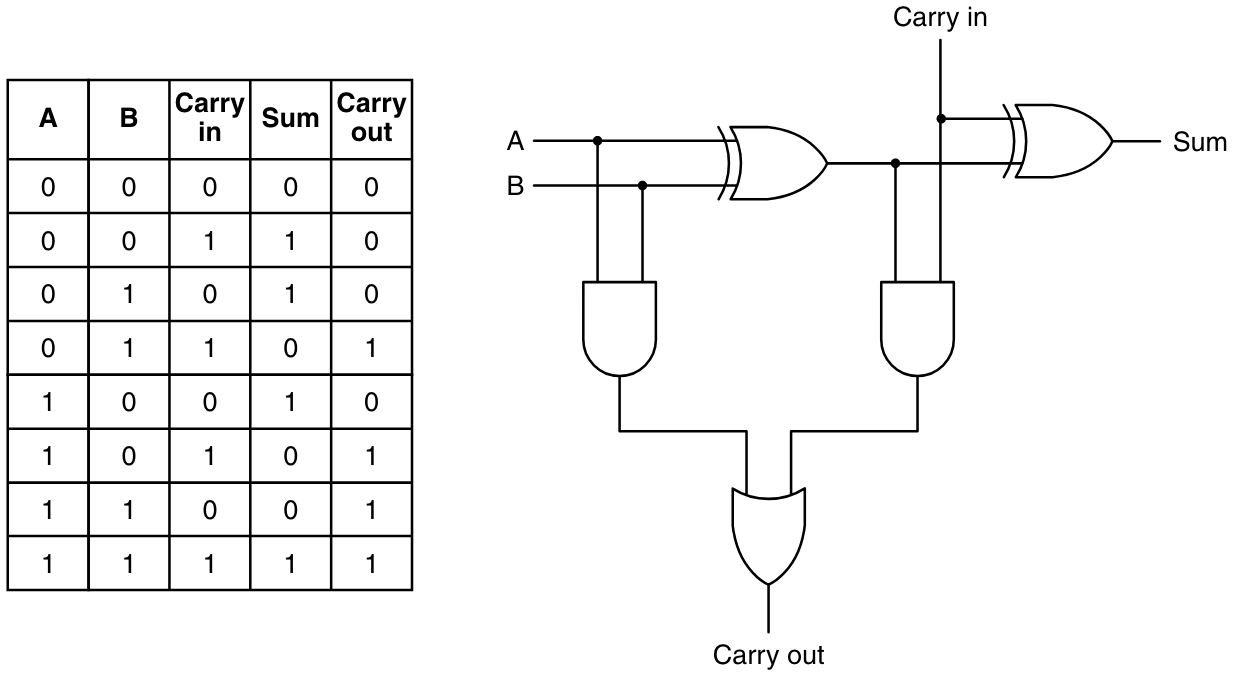

加法器

这里研究把二进制位当二进制数并实现加法的电路,这里研究两种“1位二进制”的加法单元:

1) 半加器:半加器的输入为2个二进制位,输出为“和”与进位标志。具体如上图所示,当两个二进制位都为1的时候,和为0,并发出进位信号。其他情况就是普通的求和;

2) 全加器:全加器比半加器多了进位输入。这样的话输入就等于有3个,当进位输入等于1时,等价于做2次加法,所以1个全加器由2个半加器组成。这2个半加器如果产生2个进位信息,则可以只用1个进位信息描述(之后实现加法器就明白了)。当输入和进位输入中有3个1时则和为1,进位输出为1,当输入和进位输入中有2个1时,则和为0,进位输出为1;

用于计算2个16位数加法的行波进位加法器而言,其需要16个全加器,其中第k个全加器用于计算两个16位数的第k位的和。这16个全加器之间唯一的连接关系就是第k个全加器的进位输出要作为第k+1个全加器的进位输入。这里还剩下最低位的进位输入和最高位的进位输出没有被使用,先不去管它们。可以发现这种加法器中的每个加法器之间必须要串行工作(虽然它们已经足够快了),也就是说只有在第k个全加器完成了计算,才能够让进位输出产生正确的信号时才能开始第k+1个全加器的工作(或是说必须要等待足够的时间,才能得到16个位都完全正确的结果)。

然后考虑用算法设计中的分而治之的策略做“优化”,所以这里先把16位行波进位加法器拆成3个8位行波进位加法器,3者的功能分别是最低位进位输入为1的算前8位的加法器(U0)、最低位进位输入为0的算前8位的加法器(U1)、算后8位的加法器(U)。然后把16位数分为2半,让3者并行执行。当U计算出结果后,根据U是否进位选择将U1,U或U0,U拼接为最终的和。这种方案称为选择进位加法器,其相比行波进位加法器只需要8个全加器串行的时间,即减少了一半的时间。

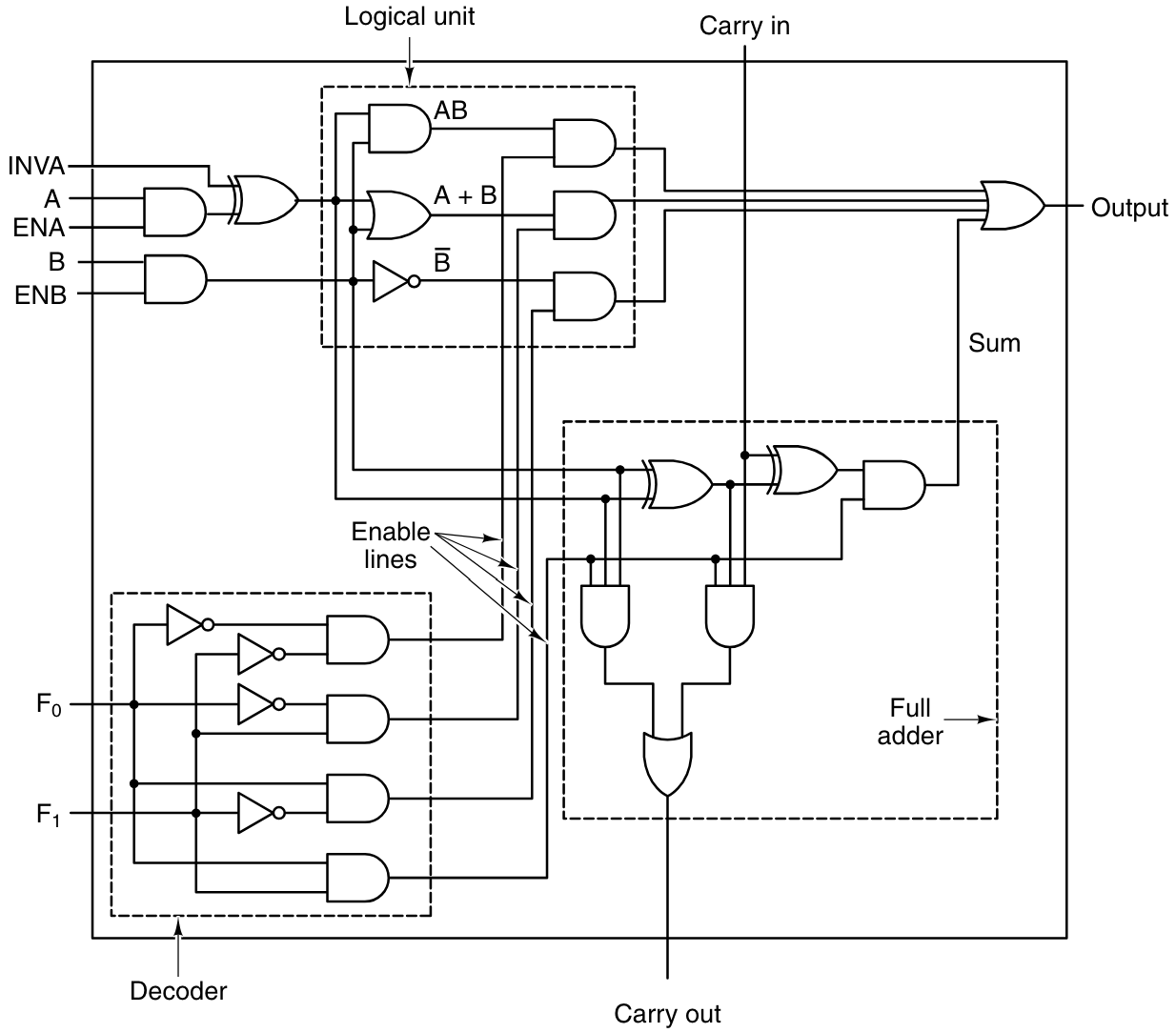

算术逻辑部件(ALU)

CPU中的ALU用于提供逻辑运算(比如与或非)与算术运算(比如二进制加减)的能力,属于1种组合逻辑电路单元。上图是1位ALU的例子,其等于把1位的全加器、逻辑与或非等运算单元组合在一起,然后通过译码器控制使用其中的哪一个运算单元。其输入中的\(F_0,F_1\)为控制信号,通过译码器控制ALU提供与、或、非、全加器中的其中1种功能,并且这些功能的输入是\(A,B\)。输入中的ENA,ENB,INVA包含一些其他用途,通常会让ENA=ENB=1,INVA=0表示将A,B不加修改的直接输入到ALU。

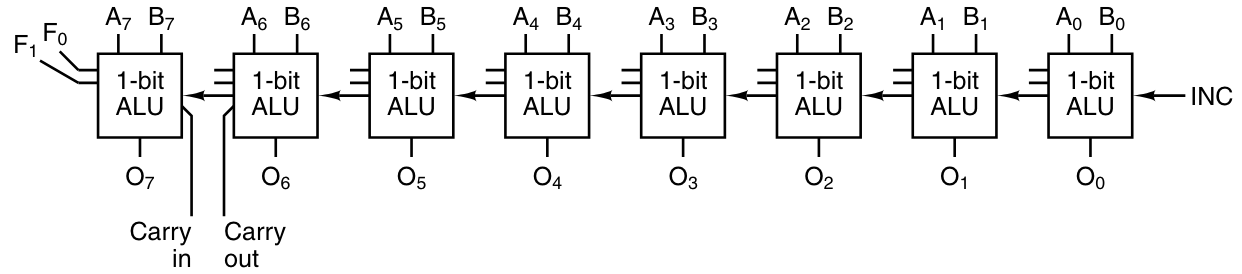

1位ALU也可像全加器那样组合起来形成任n位ALU,其组合方式如上图所示,当指令层发来“运算结果自增指令INC”时,多ALU组成的用于实现加法器的电路会将原本的A,B两数相加的结果再加上1个最低位的进位信号。在现实的CPU设计流程中,“先设计1位ALU再组合成多位ALU”的流程依然存在。

电路中的竞争与冒险

上面分析了常用的组合逻辑单元,其都假设输出和输入同时产生。但实际的电路和晶体管不可能满足这一点,首先电(电磁波)在导线上的传播速度是光速,而晶体管(门)更是有远大于光速的延迟,称为门延迟。虽然这些延迟的时间都还是很短,但还是会影响到组合逻辑电路所表达的逻辑,尤其是把组合逻辑电路放入时序逻辑电路中时,下面看2个相关的概念:

1) 竞争:竞争指门的两个输入同时改变。在光速(电流速度)尺度下,实际电路很难同时改变门的两个输入(\(A,B\)),因为接入\(A,B\)的导线可能不同,并且信号到达\(A,B\)前经过的门数量可能不同;

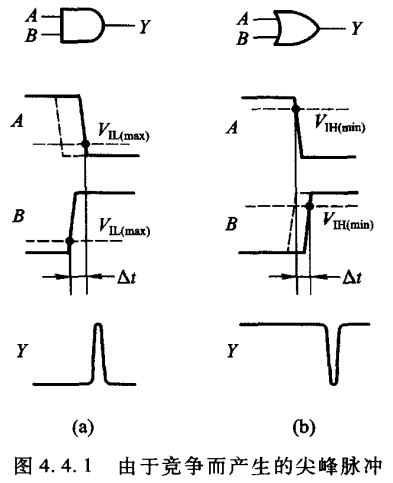

2) 冒险:冒险是指由于存在竞争,逻辑电路可能短暂的输出错误的逻辑结果。由于竞争的存在,在同时改变输入\(A,B\)时,两者的改变存在时间差,在该时间差里输入的状态可能是“\(A\)已改,\(B\)未改”或“\(B\)已改,\(A\)未改”,那么在这个时间差里门有可能会输出错误的结果,其具体例子如上图所示;

通常来说减少竞争冒险现象的影响有如下几种思路:

1) 改变电路设计:其思路是设计与原电路逻辑等价的新电路,新电路中的门不会发生竞争;

2) 引入选通脉冲:其主要思路是“等待”电路稳定,虽然输入同时改变会导致错误的电压毛刺,但如果让新输入稳定保持一段时间后再去采集新输出的话,那么新输出就不会有存在电压毛刺。实现对“等待”的控制可通过选通脉冲,等到电路其他部分稳定后,再发出选通脉冲,然后再采集新的输出;

3) 引入电容:其思路是通过电容把脉冲电压的幅度降低,使其不会突破用于判断高低电平的阈值。这种做法的副作用是会干扰正常的电平升降的时间;