数字逻辑层概述

由最底层提供给数字逻辑层的基本电路单元包括5种门(gate)。数字逻辑层主要讨论如何用各种门搭建能实现具体功能的门电路,它们被作为功能单元提供给微体系结构层。事实上很难做到仅讨论上面所规定的内容,首先必须明确更高层提供给该层的数据表示什么,否则无法设计相关的门电路,所以之后将这部分内容称为机器级数据表示,并在该层额外讨论。另外由于这里主要关注CPU的设计,所以之后不会完整讨论一些硬件的门电路实现,但为理解计算机系统的整体运转机制,仍需明确这些硬件与外界的通信规则,所以之后将这部分内容称为接口技术,并在该层额外进行讨论。

门

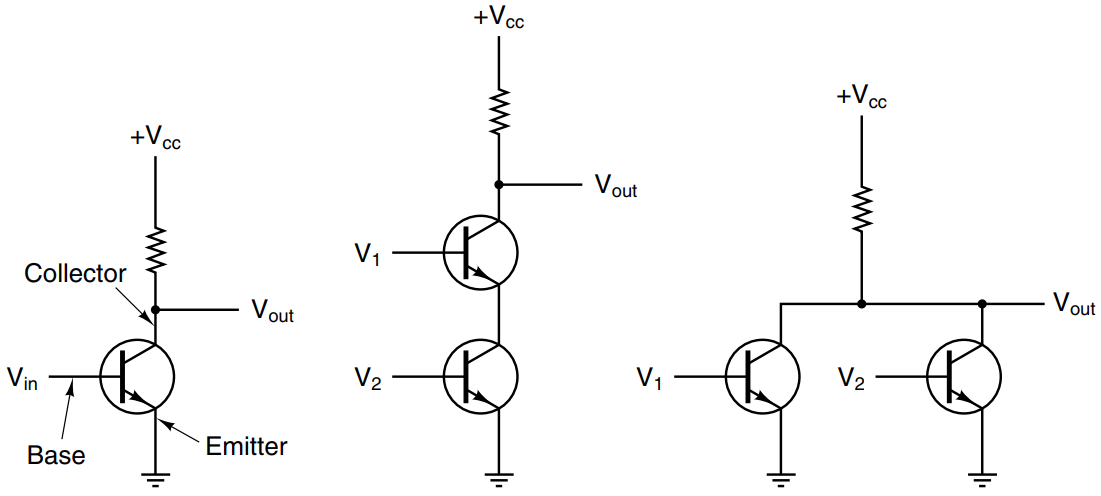

通常在数字逻辑层无需关心这5种门的内部构造,但这里还是说明一种用NPN三极管的电子开关特性构造5种门的方法。在上图第一行最左边的电路中,称对地电势0~0.5V为低电平,1~1.5V为高电平,规定\(V_{cc}\)恒为1.5V,将电势\(V_{in},V_{out}\)分别作为该电路的输入和输出。通常NPN三极管元件的导通压降在0.7V左右,当输入为低电平时,射极和集极相当于开路,\(V_{out}=V_{cc}\),所以输出为高电平,当输入为高电平时,射极和集极相当于短路,\(V_{out}=0\),所以输出为低电平。这种输入低电平输出高电平,输入高电平输出低电平的电路称为非门。通过串并联NPN三极管可得上图第一行的另外2个电路,它们都有\(V_1,V_2\)两个输入和\(V_{out}\)一个输出,分别称为与非门和或非门。最后将与非门的输出接入非门可得与门,将或非门的输出接入非门可得或门。

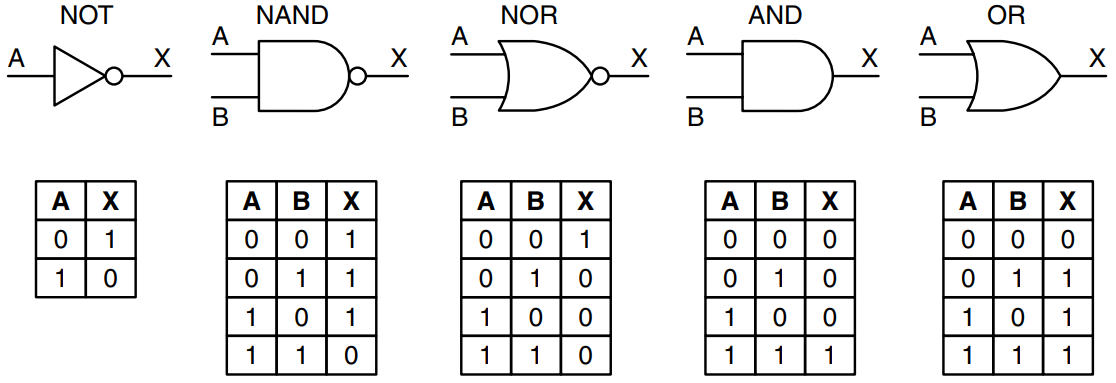

上图第二行是非门、与非门、或非门、与门、或门的电路符号。通常把低电平计为逻辑假,高电平计为逻辑真,那这5种门可用上图第三行的真值表描述。对于实际电路中的门,显然输出的变化会滞后于输入的变化,这个时间差被称为门延迟(gate delay)。历史上门其实比半导体三极管更早出现,最早的门是用继电器实现的,其门延迟非常高,现代计算机用集成电路技术将半导体三极管缩小到纳米尺寸,其门延迟是以皮秒为单位的。更低的门延迟显然能使计算机有更快的速度。

布尔代数

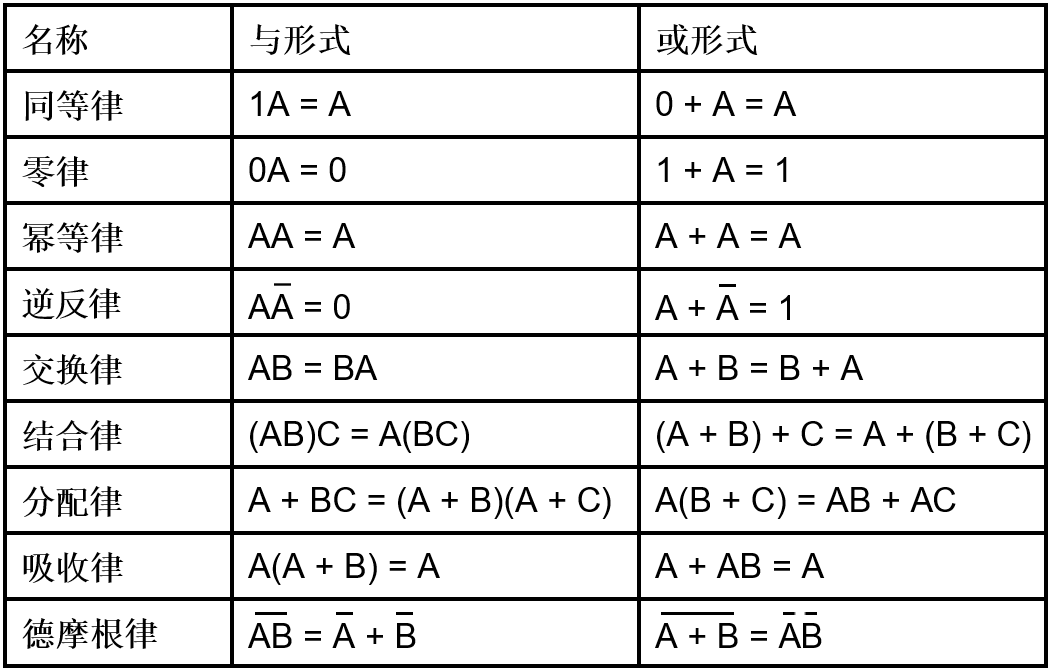

1854年英国数学家乔治·布尔提出了布尔代数(boolean algebra),其中的布尔开关代数是设计门电路的重要工具,之后会将布尔开关代数直接简称为布尔代数。布尔代数中的“数”只有真与假这两种,通常将其分别计为1与0,称为布尔值。布尔代数中的运算包括非、与、或这三种(按运算的优先级从高到低排列),它们的定义和符号表示如下:

1) 非\(A\):表示为\(\overline{A}\),其定义是“若\(A=0\)则\(\overline{A}=1\),否则\(\overline{A}=0\)”;

2) \(A\)与\(B\):表示为\(AB\),其定义是“若\(A=1\)且\(B=1\)则\(AB=1\),否则\(AB=0\)”;

3) \(A\)或\(B\):表示为\(A+B\),其定义是“若\(A=1\)或\(B=1\)则\(A+B=1\),否则\(A+B=0\)”;

在布尔代数中一般通过两种方式定义函数(布尔函数),一种是通过形如\(f(A,B,C)=\overline{A}CB+BC\)的布尔表达式定义,另一种是直接通过真值表定义。

用真值表定义的函数可以通过卡诺图等工具找到函数所对应的布尔表达式。

布尔代数的函数称为布尔函数,比如可用\(F=\overline{A}BC+BC\)的表达式形式给定多变量函数\(F\)。也可以直接通过真值表来给定函数,两个真值表相等的函数被认为是相等的。对于用真值表给定的函数,可以用卡诺图等工具找到真值表所对应的表达式。

可以发现对于任何布尔函数都可以找到其对应的门电路,反之亦然。并且可发现如果可以化简布尔表达式,那么就可用更少的门实现同样的逻辑,得到等价电路。